# IEEE 10BASE-T1S EMC Test Specification for ESD Suppression Devices

Version 1.0

| Author & Company  | Dr. Bernd Körber, FTZ Zwickau                                 |

|-------------------|---------------------------------------------------------------|

| Title             | 10BASE-T1S EMC Test Specification for ESD Suppression Devices |

| Version           | 1.0                                                           |

| Date              | August 19, 2023                                               |

| Status            | Final                                                         |

| Restriction Level | Public                                                        |

This EMC measurement specification shall be used as a standardized common scale for EMC evaluation of ESD suppression devices for 10BASE-T1S applications.

# **Version Control of Document**

| Version | Author    | Description                                                    | Date     |

|---------|-----------|----------------------------------------------------------------|----------|

| 0.1     | B. Körber | Initial version                                                | 28/02/22 |

| 0.2     | B. Körber | Parasitic capacitance measurement added                        | 11/09/22 |

|         |           | Component values for common mode termination used at           |          |

|         |           | ESD discharge current measurement changed                      |          |

| 0.3     | B. Körber | Section Measurement of parasitic capacitance reworked for      | 17/01/23 |

|         |           | better reference of single-line ESD protection devices         |          |

|         |           | <ul> <li>Figure 5.7 corrected</li> </ul>                       |          |

|         |           | <ul> <li>Test condition for ESD damage test changed</li> </ul> |          |

| 0.4     | B. Körber | Verification procedure for ESD discharge current               | 11/03/23 |

|         |           | measurement test setup added                                   |          |

|         |           | Time definition for current shape in Figure A-4 improved       |          |

|         |           | Explanation for reference current in figure A-4 added          |          |

| 0.5     | B. Körber | Marking of previous changes removed                            | 05/04/23 |

|         |           | Typos corrected                                                |          |

| 1.0     | B. Körber | Shift to final version                                         | 08/19/23 |

# **Restriction level history of Document**

| Version | Restriction Level           | Description       | Date     |

|---------|-----------------------------|-------------------|----------|

| 0.1     | OPEN Technical Members Only | Technical Members | 28/02/22 |

| 0.2     | OPEN Technical Members Only | Technical Members | 11/09/22 |

| 0.3     | OPEN Technical Members Only | Technical Members | 17/01/23 |

| 0.4     | OPEN Technical Members Only | Technical Members | 11/03/23 |

| 0.5     | OPEN Technical Members Only | Technical Members | 05/04/23 |

| 1.0     | Public                      |                   | 08/19/23 |

# **Contents**

| Foreword (Disclaimer)       |                                    |

|-----------------------------|------------------------------------|

| Introduction                |                                    |

| Abbreviation/Symbols        | 8                                  |

| 1 Scope                     | g                                  |

| 2 Normative references      | <u></u>                            |

| 3 Terms and Definitions     | <u>C</u>                           |

| 4 General                   |                                    |

| 5 Test and measurement      |                                    |

|                             |                                    |

|                             | capacitance                        |

|                             | nethod11                           |

|                             | ance analyzer measurement method14 |

| 5.3 S-parameter measureme   | nt mixed mode                      |

| •                           |                                    |

| 5.3.2 Test procedure and    | parameters19                       |

| •                           |                                    |

| 5.4.1 Test setup            | 21                                 |

| · ·                         | parameters23                       |

|                             | asurement                          |

| -                           |                                    |

| -                           | parameters28                       |

| •                           | ng effect at RF immunity tests30   |

| •                           | 30                                 |

| -                           | parameters32                       |

|                             | ests                               |

| A.1 Parasitic capacitance   |                                    |

| •                           | nt mixed mode                      |

| •                           |                                    |

| A.4 ESD Discharge Current M | easurement36                       |

| A.5 Test of unwanted Clampi | ng Effect at RF Immunity Tests     |

| Annex                       |                                    |

## Foreword (Disclaimer)

#### **OPEN Alliance Specification Copyright Notice and Disclaimer**

#### A. OPEN Specification Ownership and Usage Rights

As between OPEN Alliance and OPEN Alliance Members whose contributions were incorporated in this OPEN Specification (the "Contributing Members"), the Contributing Members own the worldwide copyrights in and to their given contributions. Other than the Contributing Members' contributions, OPEN Alliance owns the worldwide copyrights in and to compilation of those contributions forming this OPEN Specification. For OPEN Alliance Members (as that term is defined in the OPEN Alliance Bylaws), OPEN Alliance permits the use of this OPEN Specification on the terms in the OPEN Alliance Intellectual Property Rights Policy and the additional applicable terms below. For non-members of OPEN Alliance, OPEN Alliance permits the use of this OPEN Specification on the terms in the OPEN Alliance Specification License Agreement (available here: <a href="http://www.opensig.org/Automotive-Ethernet-Specifications/">http://www.opensig.org/Automotive-Ethernet-Specifications/</a>) and the additional applicable terms below. The usage permissions referenced and described here relate only to this OPEN Specification and do not include or cover a right to use any specification published elsewhere and referred to in this OPEN Specification. By using this OPEN Specification, you hereby agree to the following terms and usage restrictions:

#### A.i. Rights and Usage Restrictions Specific to OPEN Alliance Members

FOR OPEN ALLIANCE MEMBERS ONLY: In addition to the usage terms and restrictions granted to Members in the OPEN Alliance Intellectual Property Rights Policy, Members' use of this OPEN Specification is subject this Copyright Notice and Disclaimer. Members of OPEN Alliance have the right to use this OPEN Specification solely (i) during the term of a Member's membership in OPEN Alliance and subject to the Member's continued membership in good standing in OPEN Alliance; (ii) subject to the Member's continued compliance with the OPEN Alliance governance documents, Intellectual Property Rights Policy, and the applicable OPEN Alliance Promoter or Adopter Agreement, as applicable; and (iii) for internal business purposes and solely to use the OPEN Specification for implementation of this OPEN Specification in the Member's products and services, but only so long as Member does not distribute, publish, display, or transfer this OPEN Specification to any third party, except as expressly set forth in Section 11 of the OPEN Alliance Intellectual Property Rights Policy. Except and only to the extent required to use this OPEN Specification internally for implementation of this OPEN Specification in Member's products and services, Member shall not modify, alter, combine, delete portions of, prepare derivative works of, or create derivative works based upon this OPEN Specification. If Member creates any modifications, alterations, or other derivative works of this OPEN Specification as permitted to use the same internally for implementation of this OPEN Specification in Member's products and services, all such modifications, alterations, or other derivative works shall be deemed part of, and licensed to such Member under the same restrictions as, this OPEN Specification. For the avoidance of doubt, Member shall not include all or any portion of this OPEN Specification in any other technical specification or technical material, product manual, marketing material, or any other material without OPEN Alliance's prior written consent. All rights not expressly granted to Member in the OPEN Alliance Intellectual Property Rights Policy are reserved;

#### A.ii. Rights and Usage Restrictions Specific to Non-members of OPEN Alliance

FOR NON-MEMBERS OF OPEN ALLIANCE ONLY: Use of this OPEN Specification by anyone who is not a Member in good standing of OPEN Alliance is subject to your agreement to the OPEN Alliance Specification License Agreement (available here: <a href="http://www.opensig.org/Automotive-Ethernet-Specifications/">http://www.opensig.org/Automotive-Ethernet-Specifications/</a>) and the additional terms in this Copyright Notice and Disclaimer. Non-members have the right to use this OPEN Specification solely (i) subject to the non-member's continued compliance with the OPEN Alliance Specification License Agreement; and (ii) for internal business purposes and solely to use the OPEN Specification for

implementation of this OPEN Specification in the non-member's products and services, but only so long as non-member does not distribute, publish, display, or transfer this OPEN Specification to any third party, unless and only to the extent expressly set forth in the OPEN Alliance Specification License Agreement. Except and only to the extent required to use this OPEN Specification internally for implementation of this OPEN Specification in non-member's products and services, non-member shall not modify, alter, combine, delete portions of, prepare derivative works of, or create derivative works based upon this OPEN Specification. If non-member creates any modifications, alterations, or other derivative works of this OPEN Specification as permitted to use the same internally for implementation of this OPEN Specification in non-member's products and services, all such modifications, alterations, or other derivative works shall be deemed part of, and licensed to such non-member under the same restrictions as, this OPEN Specification. For the avoidance of doubt, non-member shall not include all or any portion of this OPEN Specification in any other technical specification or technical material, product manual, marketing material, or any other material without OPEN Alliance's prior written consent. All rights not expressly granted to non-member in the OPEN Alliance Specification License Agreement are reserved.

#### B. Terms Applicable to both Members and Non-members of OPEN Alliance

#### B.i. Patents, Trademarks, and other Rights:

OPEN Alliance has received no Patent Disclosure and Licensing Statements related to this OPEN Specification. Therefore, this OPEN Specification contains no specific disclaimer related to third parties that may require a patent license for their Essential Claims. Having said that, the receipt of this OPEN Specification shall not operate as an assignment of or license under any patent, industrial design, trademark, or other rights as may subsist in or be contained in or reproduced in this OPEN Specification; and the implementation of this OPEN Specification could require such a patent license from a third party. You may not use any OPEN Alliance trademarks or logos without OPEN Alliance's prior written consent.

#### **B.ii.** Disclaimers and Limitations of Liability:

THIS OPEN SPECIFICATION IS PROVIDED ON AN "AS IS" BASIS, AND ALL REPRESENTATIONS, WARRANTIES, AND GUARANTEES, EITHER EXPLICIT, IMPLIED, STATUTORY, OR OTHERWISE, ARE EXCLUDED AND DISCLAIMED UNLESS (AND THEN ONLY TO THE EXTENT THEY ARE) MANDATORY UNDER LAW. ACCORDINGLY, OPEN ALLIANCE AND THE CONTRIBUTING MEMBERS MAKE NO REPRESENTATIONS OR WARRANTIES OR GUARANTEES WITH REGARD TO THIS OPEN SPECIFICATION OR THE INFORMATION (INCLUDING ANY SOFTWARE) CONTAINED HEREIN. OPEN ALLIANCE AND ALL CONTRIBUTING MEMBERS HEREBY EXPRESSLY DISCLAIM ANY AND ALL SUCH EXPRESS, IMPLIED, STATUTORY, AND ALL OTHER REPRESENTATIONS, WARRANTIES, AND GUARANTEES, INCLUDING WITHOUT LIMITATION ANY AND ALL WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR USE, TITLE, NON-INFRINGEMENT OF OR ABSENCE OF THIRD PARTY RIGHTS, AND/OR VALIDITY OF RIGHTS IN THIS OPEN SPECIFICATION; AND OPEN ALLIANCE AND THE CONTRIBUTING MEMBERS MAKE NO REPRESENTATIONS AS TO THE ACCURACY OR COMPLETENESS OF THIS OPEN SPECIFICATION OR ANY INFORMATION CONTAINED HEREIN. WITHOUT LIMITING THE FOREGOING, OPEN ALLIANCE AND/OR CONTRIBUTING MEMBERS HAS(VE) NO OBLIGATION WHATSOEVER TO INDEMNIFY OR DEFEND YOU AGAINST CLAIMS RELATED TO INFRINGEMENT OR MISAPPROPRIATION OF INTELLECTUAL PROPERTY RIGHTS.

OPEN ALLIANCE AND CONTRIBUTING MEMBERS ARE NOT, AND SHALL NOT BE, LIABLE FOR ANY LOSSES, COSTS, EXPENSES, OR DAMAGES OF ANY KIND WHATSOEVER (INCLUDING WITHOUT LIMITATION DIRECT, INDIRECT, SPECIAL, INCIDENTAL, CONSEQUENTIAL, PUNITIVE, AND/OR EXEMPLARY DAMAGES) ARISING IN ANY WAY OUT OF USE OR RELIANCE UPON THIS OPEN SPECIFICATION OR ANY INFORMATION HEREIN.

NOTHING IN THIS DOCUMENT OPERATES TO LIMIT OR EXCLUDE ANY LIABILITY FOR FRAUD OR ANY OTHER LIABILITY WHICH IS NOT PERMITTED TO BE EXCLUDED OR LIMITED BY OPERATION OF LAW.

#### B.iii. Compliance with Laws and Regulations:

NOTHING IN THIS DOCUMENT OBLIGATES OPEN ALLIANCE OR CONTRIBUTING MEMBERS TO PROVIDE YOU WITH SUPPORT FOR, OR RELATED TO, THIS OPEN SPECIFICATION OR ANY IMPLEMENTED PRODUCTS OR SERVICES. NOTHING IN THIS OPEN SPECIFICATION CREATES ANY WARRANTIES OR GUARANTEES, EITHER EXPRESS OR IMPLIED, STATUTORY OR OTHERWISE, REGARDING ANY LAW OR REGULATION. OPEN ALLIANCE AND CONTRIBUTING MEMBERS EXPRESSLY DISCLAIM ALL LIABILITY, INCLUDING WITHOUT LIMITATION, LIABILITY FOR NONCOMPLIANCE WITH LAWS, RELATING TO USE OF THE OPEN SPECIFICATION OR INFORMATION CONTAINED HEREIN. YOU ARE SOLELY RESPONSIBLE FOR THE COMPLIANCE OF IMPLEMENTED PRODUCTS AND SERVICES WITH ANY SUCH LAWS AND REGULATIONS, AND FOR OBTAINING ANY AND ALL REQUIRED AUTHORIZATIONS, PERMITS, AND/OR LICENSES FOR IMPLEMENTED PRODUCTS AND SERVICES RELATED TO SUCH LAWS AND REGULATIONS WITHIN THE APPLICABLE JURISDICTIONS.

IF YOU INTEND TO USE THIS OPEN SPECIFICATION, YOU SHOULD CONSULT ALL APPLICABLE LAWS AND REGULATIONS. COMPLIANCE WITH THE PROVISIONS OF THIS OPEN SPECIFICATION DOES NOT CONSTITUTE COMPLIANCE TO ANY APPLICABLE LEGAL OR REGULATORY REQUIREMENTS. IMPLEMENTERS OF THIS OPEN SPECIFICATION ARE SOLELY RESPONSIBLE FOR OBSERVING AND COMPLYING WITH THE APPLICABLE LEGAL AND REGULATORY REQUIREMENTS. WITHOUT LIMITING THE FOREGOING, YOU SHALL NOT USE, RELEASE, TRANSFER, IMPORT, EXPORT, AND/OR RE-EXPORT THIS OPEN SPECIFICATION OR ANY INFORMATION CONTAINED HEREIN IN ANY MANNER PROHIBITED UNDER ANY APPLICABLE LAWS AND/OR REGULATIONS, INCLUDING WITHOUT LIMITATION U.S. EXPORT CONTROL LAWS.

**B.iv.** Automotive Applications Only: Without limiting the foregoing disclaimers or limitations of liability in any way, this OPEN Specification was developed for automotive applications only. This OPEN Specification has neither been developed, nor tested for, non-automotive applications.

## B.v. Right to Withdraw or Modify:

OPEN Alliance reserves the right to (but is not obligated to) withdraw, modify, or replace this OPEN Specification at any time, without notice.

© [2022] OPEN Alliance. This document also contains contents, the copyrights of which are owned by third parties who are OPEN Alliance Contributing Members. Unauthorized Use Strictly Prohibited. All Rights Reserved.

#### Introduction

The IEEE 802.3cg standard defines a 10 Mbit/s Ethernet communication over an unshielded single pair of conductors and separate the two systems 10BASE-T1S and 10BASE-T1L. The 10BASE-T1S implementation covers a half duplex communication using a CSMA/CD for point to point channel and the optional functionalities full duplex communication for a point to point channel and a half duplex communication for a so called mixing segment (or multidrop mode) with at least 8 nodes and 25 m length of bus lines. In any case, the bus cable is terminated with the line impedance of  $100~\Omega$  at both ends of the channel. As an optional feature to enable a deterministic access time for each bus node in a mixing segment the new access method PLCA is overlaid to the CSMA/CD system. Due to the high communication rate of 10BASE-T1 and the intended use of unshielded twisted pair cable, a high risk of EMC problems is expected. For this reason, an EMC optimization of all components of the Ethernet physical layer is required.

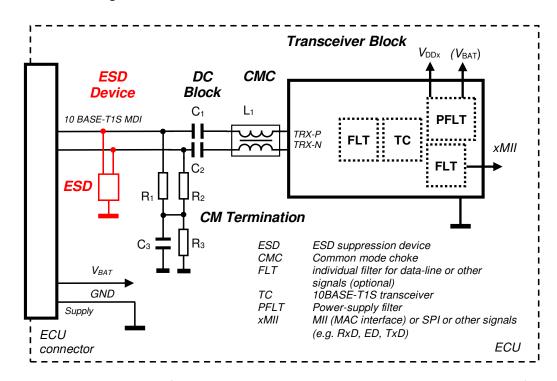

An ESD suppression device can be used to increase the ESD robustness of 10BASE-T1S Ethernet transceivers according to [1] and can have a significant effect on EMC test results in communication networks. In principle there are two possible positions of ESD suppression device implementation within an Ethernet interface: between the transceiver and the CMC or between the MDI connector and the common mode termination network as described in Figure 1.

Figure 1: Arrangement of ESD suppression device within the 10BASE-T1S MDI interface

This EMC measurement specification is focused on evaluation of the ESD suppression device characteristics related to high frequency and functional aspects as well as ESD.

# Abbreviation/Symbols

BIN

Bus Interface Network

CMC

Common Mode Choke

CMR

Common Mode Rejection

CMT

Common Mode Termination

**DCMR** Differential to Common Mode Rejection, common mode single ended measured

ESD Electro Static Discharge

IL Insertion Loss

MDI Medium Dependent Interface

**RF** Radio Frequency

RL Return Loss

S-Parameter Scattering Parameter

VNA Vector Network Analyzer

TLP Transmission Line Pulse

## 1 Scope

This document specifies test and measurement methods for characterization of ESD suppression device intended to use for the position between MDI connector and common mode termination network within the 10BASE-T1S interface according to Figure 1. It contains definitions for test methods, test conditions, performance criteria, test procedures, test setups, test boards and recommended limits and covers

- evaluation of datasheet parameters;

- parasitic capacitance;

- S-Parameter measurement mixed mode;

- ESD damage test;

- test of unwanted clamping effect at RF immunity tests;

- impact to ESD discharge current in a defined 10BASE-T1S network.

It shall be used for evaluation of ESD suppression devices or passive components with internal ESD suppression unit (e.g. combination of ESD suppression and common mode termination circuit).

#### 2 Normative references

The following documents are referred to in the text in such a way that some or all of their content constitutes requirements of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

- [1] IEEE P802.3cg<sup>™</sup>: Physical Layer Specifications and Management Parameters for 10 Mb/s Operation and Associated Power Delivery over a Single Balanced Pair of Conductors

- [2] IEC 62615, Electrostatic discharge sensitivity testing Transmission line pulse (TLP) Component level

- [3] ISO 10605, Road vehicles Test methods for electrical disturbances from electrostatic discharge

- [4] OPEN ALLIANCE, IEEE 10BASE-T1S EMC Test Specification for Common mode chokes

- [5] OPEN ALLIANCE, IEEE 10BASE-T1S EMC Test Specification for Transceivers

#### 3 Terms and Definitions

For the purposes of this document, the terms and definitions given in 2 and following apply.

ISO and IEC maintain terminological databases for use in standardization at the following addresses:

- ISO Online browsing platform: available at https://www.iso.org/obp;

- IEC Electropedia: available at http://www.electropedia.org.

#### 4 General

The intention of this document is to evaluate the EMC performance of ESD suppression devices intended to use for 10BASE-T1S Ethernet interfaces. The final judgment of the tested device is left to the customer.

#### 5 Test and measurement

#### 5.1 General definitions

All tests are performed for standard room temperature (23 °C +/- 3 K).

A printed circuit board with RF board-to-coax connectors should be used for RF parameter related tests. To ensure reliable RF parameters, a test board with at least two layers with enlarged GND reference plane is required. The traces on the test board should be designed as 50 ( $\pm$  5)  $\Omega$  single ended transmission lines with a length as short as possible.

The test board design and the method of connecting the ESD suppression device with the test board shall provide high accuracy and reproducible test results.

All test are defined at a two-line ESD suppression device used in a 10BASE-T1S MDI. If the ESD suppression device has more than two lines, the test setup should be adapted accordingly. The test of single-line ESD suppression devices shall be performed with a combination of two devices of the same type.

Prior to performing any RF and ESD tests, the S-Parameter measurements shall be performed on a minimum of 10 samples.

The following parameters for ESD suppression device shall be ensured and documented in the datasheet.

| Parameter                               | Target Value                                                                                                                                                                    |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Working direction                       | bi-directional                                                                                                                                                                  |

| Operation voltage (V <sub>DCmax</sub> ) | ≥ 24 V                                                                                                                                                                          |

| ESD trigger voltage                     | ≥ 100 V                                                                                                                                                                         |

| ESD robustness                          | +/- 15kV contact discharge for unpowered device using discharge module according to ISO 10605 (discharge storage capacitor C = 150 pF and discharge resistor R = 330 $\Omega$ ) |

| Minimum number of discharges            | > 1000                                                                                                                                                                          |

| TLP characteristic according to [2]     | I/V characteristics                                                                                                                                                             |

Table 5-1: Target values for ESD suppression device

The given target values for operation voltage and ESD trigger voltage are related to the position of ESD protection device within the BIN as given in Figure 1.

#### 5.2 Measurement of parasitic capacitance

In general, the parasitic capacitance of ESD suppression device is measured between the two pins that connect the MDI lines of a 10BASE-T1S interface while the GND pin of the device is connected to common GND. In consequence, the resulting measured parasitic capacitance for single-line ESD suppression devices is half of the single device value itself.

The parasitic capacitance should be measured ether with VNA measurement method or with LCR meter / impedance analyzer measurement method.

#### **5.2.1** VNA measurement method

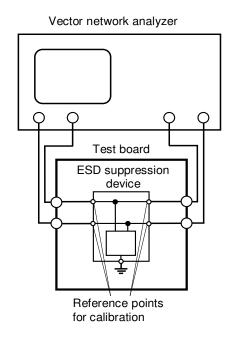

#### **5.2.1.1** Test setup

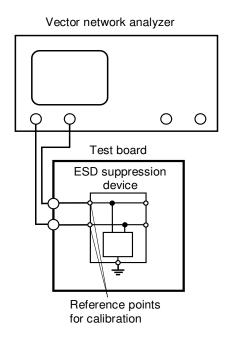

The test setup for measuring the parasitic capacitance consists of a VNA in combination with a special test board (adapter test board). The test board is included into the test setup during VNA calibration. The reference points for calibration are defined to the pads of the ESD suppression device at the test board.

Figure 5-1: Test setup for parasitic capacitance measurement for VNA method

The test equipment definitions are the following:

- vector network analyzer;

- test board parasitic capacitance.

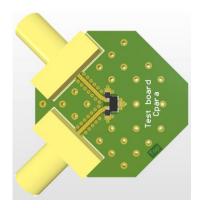

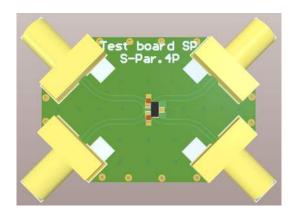

The connecting traces of the test board from RF connectors to the ESD suppression device should be routed symmetrically at 45° to decrease parasitic inductive coupling. An example for test board is given in Figure 5-2.

Figure 5-2: Example of test board parasitic capacitance measurement for VNA method, top layer

The test board symmetry and calibration accuracy should be validated with measurement of an open-circuit (without DUT). The remaining open-circuit capacitance should not exceed 50 fF.

## **5.2.1.2** Test procedure and parameters

The test procedure and parameters are defined in Table 5-7.

| Item             | Parameter                                                                        |  |

|------------------|----------------------------------------------------------------------------------|--|

| Frequency range: | 1 MHz to 100 MHz                                                                 |  |

| S-parameter per  | $S_{11}$ , Re + j Im / ESD suppression device line 1                             |  |

| single path:     | S <sub>22</sub> , Re + j Im / ESD suppression device line 2                      |  |

|                  | $S_{21}$ , Re + j Im / ESD suppression device line 1 to line 2                   |  |

|                  | $S_{12}$ , Re + j Im / ESD suppression device line 2 to line 1                   |  |

| VNA measurement  | port definitions:                                                                |  |

| circuit:         | logic port 1: physical port 1 / ESD suppression device line 1                    |  |

|                  | logic port 2: physical port 2 / ESD suppression device line 2                    |  |

|                  | Test board  Logical port 1  VNA port 1 (50 Ω)  Logical port 2  VNA port 2 (50 Ω) |  |

| Calculation<br>method: | 1. | Calculate Y-Parameters from S-Parameters: $ [S] = \begin{bmatrix} s_{11} & s_{12} \\ s_{21} & s_{22} \end{bmatrix} \implies [Y] = \begin{bmatrix} Y_{11} & Y_{12} \\ Y_{21} & Y_{22} \end{bmatrix} $ |

|------------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |    | Note: All calculations should be performed using raw or linearly interpolated data, to avoid inaccuracy introduced by e.g. spline interpolation or rational fitting.                                 |

|                        | 2. | Calculate the mean transfer Y-Parameter $Y_T$ : $Y_T = \frac{(Y_{21} + Y_{12})}{2} = \frac{S_{12} + S_{21}}{50 \cdot (1 + S_{11} - S_{12} \cdot S_{21} + S_{22} + S_{11} \cdot S_{22})}$             |

|                        | 3. | Calculate the parasitic capacitance $C_{para}(f)$ while extracting the negative imaginary part of $Y_T$ : $C_{para}(f) \approx \frac{Im(-Y_T)}{2\pi f}$                                              |

|                        | 4. | The resulting value $C_{para\_max}$ is the maximum value of $C_{para}$ (f) in the frequency range from f = 5 MHz to f = 15 MHz.                                                                      |

Table 5-2: Test procedure and parameters for parasitic capacitance measurements at ESD suppression device using VNA method

The tests should be performed at 10 samples and documented in a diagram with  $C_{para}$  (f) and  $C_{para_{max}}$  according to the scheme given in Table 5-3. Recommended limits for evaluation are given in Annex A.1.

| Test | Item            | Sample     |

|------|-----------------|------------|

| CP1  | $C_{para\_max}$ | 10 samples |

Table 5-3: Required parasitic capacitance measurements for ESD suppression device

EMC Test Specification for 10BASE-1S ESD Suppression Devices

#### 5.2.2 LCR meter or impedance analyzer measurement method

#### **5.2.2.1 Test setup**

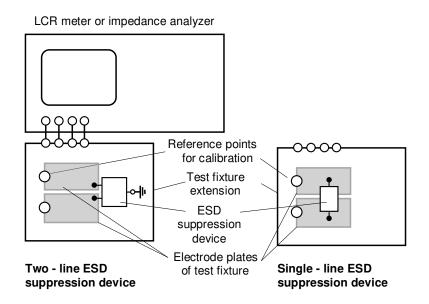

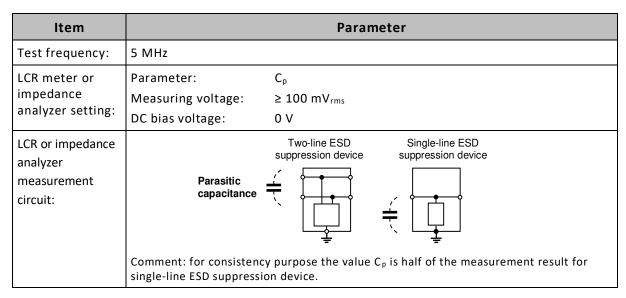

The test setup for measuring the parasitic capacitance consists of a LCR meter or an impedance analyzer in combination with a special test fixture extension, direct mounted to the measuring device. The reference points for calibration are defined to electrode plates at the test fixture extension the contact the ESD suppression device. As shown in Figure 5-3 two-line ESD protection devices and single-line ESD protection devices can be measured in a different way.

Figure 5-3: Test setup for parasitic capacitance measurement for LCR meter or impedance analyzer method

The test equipment definitions are the following:

- LCR meter or impedance analyzer;

- test fixture extension, direct mounted to the measuring device.

#### 5.2.2.2 Test procedure and parameters

The test procedure and parameters are defined in Table 5-4.

Table 5-4: Test procedure and parameters for parasitic capacitance measurements at ESD suppression device using LCR meter or impedance analyzer method

The tests should be performed at 10 samples and documented. Recommended limits for evaluation are given in Annex A.1.

| Test | Item                  | Sample     |

|------|-----------------------|------------|

| CP1  | C <sub>para_max</sub> | 10 samples |

Table 5-5: Required parasitic capacitance measurements for CMC

#### 5.3 S-parameter measurement mixed mode

#### 5.3.1 Test setup

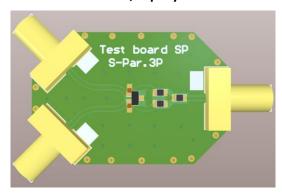

The test setup for measuring the mixed mode *S*-parameters consists of a 4-port VNA in combination with a special test board (adapter test board). The test board is included into the test setup during VNA calibration. The reference points for calibration are defined to the pads of the ESD suppression device at the test board.

Figure 5-4: Test setup for S-parameter measurements

The test equipment definitions are the following:

- 4-port vector network analyzer;

- test board S-parameter mixed mode (4-port) and

- test board S-parameter single ended (3-port).

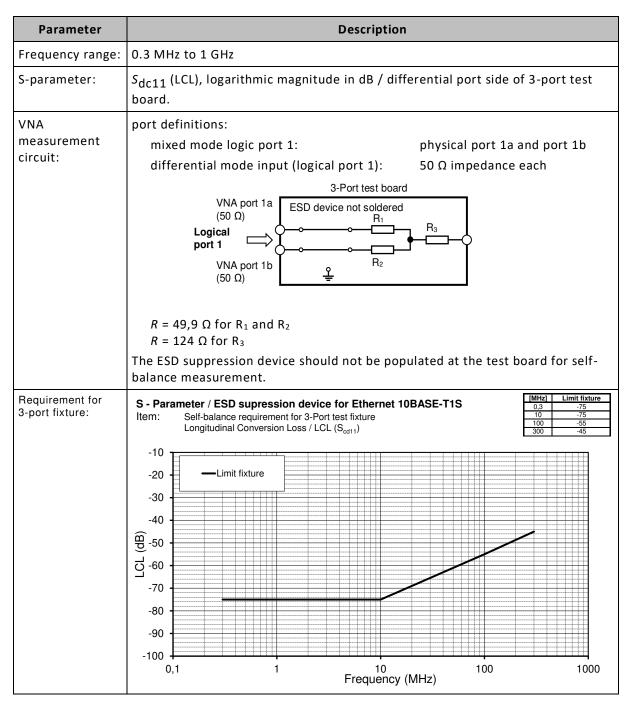

For the S-parameter 3-port test board, additional specific requirements are defined. The 3-port test board with soldered RF connectors used for balance measurement should have a very high grade of self-balance. To ensure the test board self-balance characteristic of symmetrical network at logical port 2 (common mode), the traces between the DUT and all resistors (R1, R2 and R3) must be kept highly symmetric and as short as possible. To verify the test board self-balance characteristic, the test parameter and requirements given in Table 5-6 are defined.

Examples for test boards are given in Figure 5-5 and Figure 5-6.

Figure 5-5: Example of test board 4-port S-parameter measurement for ESD suppression device – mixed mode, top layer

Figure 5-6: Example of test board 3-port S-parameter measurement ESD suppression device – single ended, top layer

Table 5-6: Test procedure and parameters for 3-port test board characterization for ESD suppression device

# 5.3.2 Test procedure and parameters

The test procedure and parameters are defined in Table 5-7.

| Item                         | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Frequency range:             | 0.3 MHz to 1 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

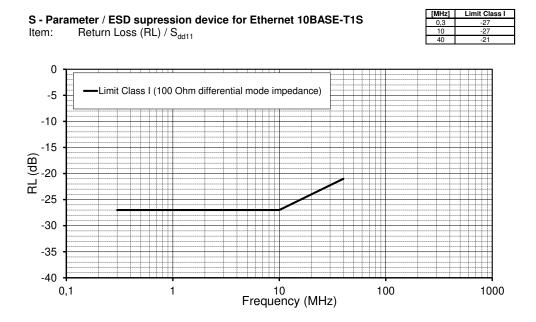

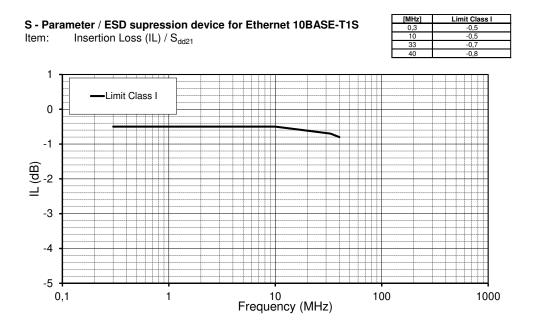

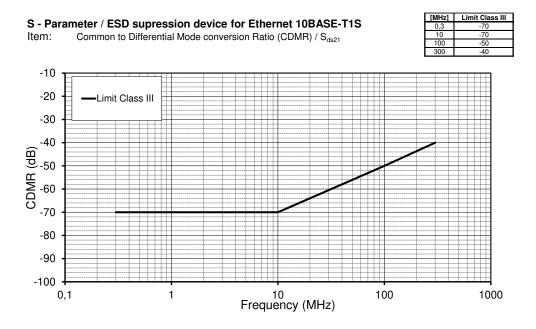

| S-parameter per single path: | 4-port parameters $S_{\rm dd11}$ (RL), logarithmic magnitude in dB $S_{\rm dd21}$ (IL), logarithmic magnitude in dB 3-port parameters $S_{\rm sd21}$ (DCMR), logarithmic magnitude in dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VNA measurement circuit:     | port definitions:     mixed mode logic port 1: physical port 1a and port 1b     mixed mode logic port 2: physical port 2a and port 2b  4-port measurements / $S_{\rm dd11}$ and $S_{\rm dd21}$ mixed mode:  50 $\Omega$ input impedance at each measurement port  Test board  VNA port 1a  (50 $\Omega$ )  Logical port 1  VNA port 1b  (50 $\Omega$ )  Logical port 2  VNA port 2b  (50 $\Omega$ )  3-port measurements / $S_{\rm sd21}$ single ended:  differential mode input (logical port 1): common mode output (logical port 2): single ended network with 200 $\Omega$ impedance $R = (R_1 \mid  R_2  + R_3 + R_{\rm VNA} \text{ port 2a}$ VNA port 1a  (50 $\Omega$ )  Logical port 1  VNA port 1a  (50 $\Omega$ )  Logical port 1  VNA port 1a (50 $\Omega$ )  Logical port 1  VNA port 1a (50 $\Omega$ )  Logical port 1  VNA port 1a (50 $\Omega$ )  Logical port 1  VNA port 1a (50 $\Omega$ )  Logical port 1  VNA port 2a (50 Ohm) |

|                              | The accuracy of resistor values should be $\leq$ 1 %. The difference between matching resistors should be $\leq$ 0.1 %.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Table 5-7: Test procedure and parameters for S-parameter measurements at ESD suppression device

#### OPEN Alliance Inc.

The measurements should be performed and documented according to the scheme given in Table 5-8.

| Test | S-parameter              | Sample          |

|------|--------------------------|-----------------|

| S1   | S <sub>dd11</sub> (RL)   |                 |

| S2   | S <sub>dd21</sub> (IL)   | 10 samples each |

| S3   | S <sub>sd21</sub> (DCMR) |                 |

Table 5-8: Required S-parameter measurements for ESD suppression device

For each test case, the results for all 10 samples should be documented as diagram in the ESD suppression device characterization report. Recommended limits for evaluation are given in Annex A.2.

Aug-23

#### 5.4 ESD damage

#### 5.4.1 Test setup

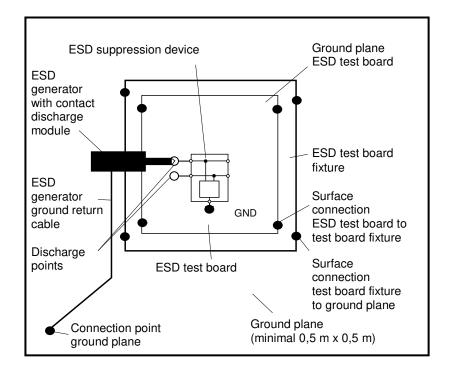

The test setup given in Figure 5-7 is used for testing the ESD robustness of ESD suppression device.

Figure 5-7: Test setup for ESD damage tests at ESD suppression device

The test equipment definitions are the following:

- ESD generator (according to ISO 10605, discharge storage capacitor C = 150 pF and discharge resistor  $R = 330 \Omega$ );

- ESD test board;

- ground plane and

- test board fixture.

The ground plane with a minimum size of  $0.5 \, \text{m} \times 0.5 \, \text{m}$  is connected to protective earth of the electrical grounding system of the test laboratory. The ESD generator ground return cable is directly connected to this ground plane. The metallic test fixture positions the ESD test board and directly connects the ESD test board ground plane to the reference ground plane. The ground connection of the test fixture is connected to ground plane with low impedance and low inductance. This surface connection should have a contact area of at least  $4 \, \text{cm}^2$ . Copper tapes can be used in addition. The tip of the ESD generator is directly contacted with one of the discharge points DP1 and DP2 of the ESD test board for testing. For this purpose, the discharge points can be implemented as rounded landing pads or vias in the layout of the ESD test board and are directly connected by a trace 15 (±5) mm with the respective pin of the ESD suppression device.

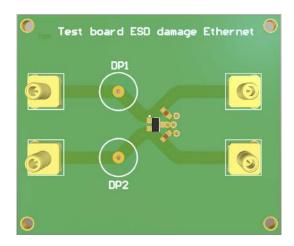

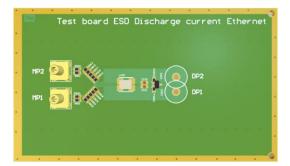

An example for ESD test board is given in Figure 5-8.

Figure 5-8: Example of ESD test board for ESD suppression device, top layer

For check of damage evaluation criteria (S-parameter), the reference points for calibration are the input of RF connector (SMA) at the test board.

To achieve a high grade of accuracy of required *S*-parameter measurements for damage evaluation, it is recommended to use the same test board for *S*-parameter and ESD tests without re-soldering the DUT.

# 5.4.2 Test procedure and parameters

The required tests and procedure are defined in Table 5-9 and should be done on one sample.

| Item                           | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Coupling of ESD:               | Direct discharge method according to ISO 10605 (discharge storage capacitor C = 150 pF and discharge resistor R = 330 $\Omega$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Test circuit:                  | Test board  ESD suppression device  DP1  DP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ESD test voltage:              | ± 8 kV, ± 15 kV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Number of discharges:          | 20 per polarity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Time between discharges:       | 5 s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Damage<br>evaluation criteria: | - degrade by more than 0,1 dB from the initial value after performing the tests for S-parameter $S_{\rm dd21}$ for frequencies $f \le 200$ MHz - degrade by more than 1 dB from the initial value after performing the tests for S-parameter $S_{\rm dd11}$ , $S_{\rm dd22}$ and $S_{\rm cd21}$ for frequencies $f \le 200$ MHz  The S-parameter measurements should be done according to 5.3. Frequency ranges or frequency spots with a level at noise floor or below the related limits of 5.3 should not be weighted for applying the damage evaluation criteria.  For simplification of measurement for check of mode conversion loss the S-parameter $S_{\rm cd21}$ is used instead of $S_{\rm sd21}$ . The setup for S-parameter $S_{\rm cd21}$ is same as used for the other required S-parameter. Because of different test circuitry for S-parameter $S_{\rm cd21}$ and $S_{\rm sd21}$ the related limit for S-parameter $S_{\rm cd21}$ is corrected by + 10 dB. |

| Test procedure:                | <ol> <li>S-parameter reference measurement before ESD test</li> <li>apply ESD discharges at DP1 (± 8 kV, 10 per polarity, 5 s delay)</li> <li>apply ESD discharges at DP2 (± 8 kV, 10 per polarity, 5 s delay)</li> <li>evaluate damage using damage evaluation criteria</li> <li>apply ESD discharges at DP1 (± 15 kV, 10 per polarity, 5 s delay)</li> <li>apply ESD discharges at DP2 (± 15 kV, 10 per polarity, 5 s delay)</li> <li>evaluate damage using damage evaluation criteria</li> <li>If a damage occurs at ± 8 kV or ± 15 kV the test should be repeated with a reduced ESD test voltage to find out the immunity threshold of the DUT. Nevertheless, applying an ESD test voltage of ± 15 kV without damage for DUT is required to pass the test.</li> </ol>                                                                                                                                                                                                 |

Table 5-9: Test parameters for ESD damage tests at ESD suppression device

The measurements should be performed and documented according to the scheme given in Table 5-10.

| Test | Discharge point | Comment | Sample    |  |

|------|-----------------|---------|-----------|--|

| E1   | DP1             | Line 1  | 2 samples |  |

| E2   | DP2             | Line 2  | 3 samples |  |

Table 5-10: Required ESD tests for damage for ESD suppression device

The ESD suppression device should withstand the ESD discharge without damage according to the damage evaluation criteria. Recommended limits are given in Annex A.3.

## 5.5 ESD discharge current measurement

## 5.5.1 Test setup

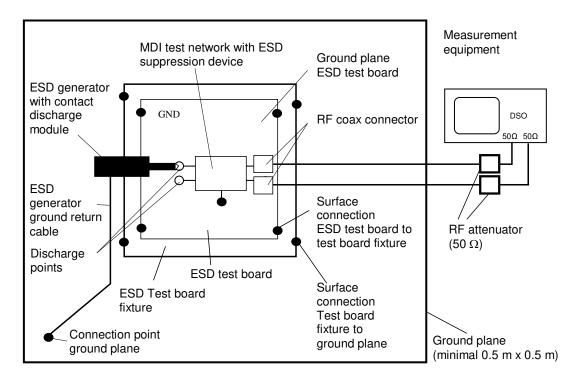

The setup given in Figure 5-9 should be used for measuring the ESD discharge current through a 10BASE-T1S transceiver simulation network if the ESD suppression device is used as a part of the MDI network.

Figure 5-9: Test setup for ESD discharge current measurement

The test equipment definitions are the following:

- ESD generator (according to ISO 10605, discharge storage capacitor C = 150 pF and discharge resistor  $R = 330 \Omega$ );

- digital storage oscilloscope (DSO, 50  $\Omega$  input impedance, minimum 1GHz analog input bandwidth);

- RF attenuator (50  $\Omega$ );

- ESD test board discharge current;

- ground plane, and

- test board fixture.

The ground plane with a minimum size of  $0.5 \, \text{m} \times 0.5 \, \text{m}$  is connected to protective earth of the electrical grounding system of the test laboratory. The ESD generator ground return cable is directly connected to this ground plane. The metallic test fixture positions the ESD test board and directly connects the ESD test board ground plane to the reference ground plane. The ground connection of the test fixture is connected to ground plane with low impedance and low inductance. This surface connection should have a contact area of at least 4 cm2. Copper tapes can be used in addition. For reduction of parasitic field coupling from ESD generator into the test circuit it is recommended to position the ESD test board with passive components on bottom side into the metallic test fixture.

#### OPEN Alliance Inc.

The tip of the ESD generator is directly contacted with one of the discharge points DP1 and DP2 of the ESD test board for testing. For this purpose, the discharge points are implemented as rounded vias in the layout of the ESD test board and are directly connected by a trace 15 (±5) mm with the respective pin of the ESD suppression device.

Shielded cables are used for connection of measurement outputs of the MDI test network on the ESD test board to the DSO's 50  $\Omega$  inputs. An additional attenuator is recommended to prevent the DSO inputs from damage. Care should be taken that the used DSO is not influenced by the ESD discharge event.

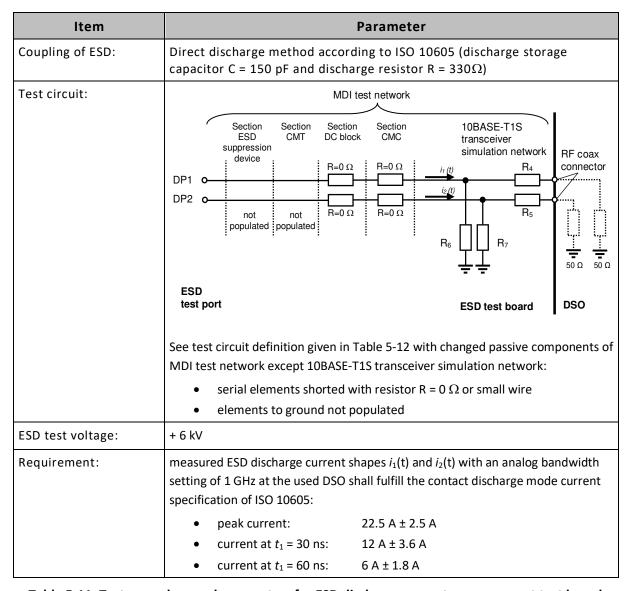

A verification of used test setup shall be performed using the test parameter and requirements defined in Table 5-11.

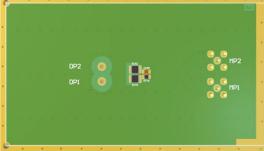

An example for ESD test board discharge current is given in Figure 5-10.

Figure 5-10: Example of ESD test board discharge current for ESD suppression device, top and bottom layer

Table 5-11: Test procedure and parameters for ESD discharge current measurement test board characterization

27

# 5.5.2 Test procedure and parameters

The required test procedure and parameters are defined in Table 5-12.

| Item                 | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Coupling of ESD:     | Direct discharge method according to ISO 10605 (discharge storage capacitor C = 150 pF and discharge resistor R = 330 $\Omega$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Test circuit:        | MDI test network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                      | ESD suppression device $CMC$ |  |  |

|                      | resistors with higher nominal value and SMD design 0603 or 0402 is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| ESD test voltage:    | $\pm$ 3 kV, $\pm$ 5 kV, $\pm$ 6 kV, $\pm$ 7 kV, $\pm$ 15 kV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Evaluation criteria: | measured ESD discharge current shapes $i_1(t)$ and $i_2(t)$ with an analog bandwidth setting of 1 GHz at the used DSO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

Table 5-12: Test procedure and parameters for ESD discharge current measurement

The tests should be performed and documented according to the scheme given in Table 5-13.

| Test | Discharge<br>point | Comment     | ESD saturation class of used CMC according to [4] | Sample         |

|------|--------------------|-------------|---------------------------------------------------|----------------|

| E1   | DP1                | Line 1      | 1                                                 |                |

| E2   | DPI                | DP1 Lille 1 | П                                                 | 2 samples each |

| E3   | DP2                | Line 2      | I                                                 | 3 samples each |

| E4   | DP2                | Lille 2     | П                                                 |                |

Table 5-13: Required current measurement for ESD suppression device

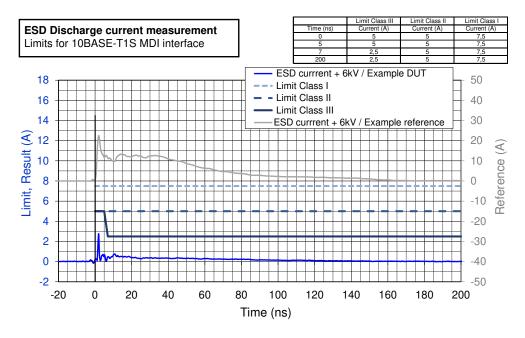

For each test case the remaining ESD discharge current waveform, measured after the MDI test network, should be recorded and documented in a diagram in the test report. The measured ESD discharge current waveform should be below the recommended limits given in Annex A.4.

# 5.6 Test of unwanted clamping effect at RF immunity tests

#### 5.6.1 Test setup

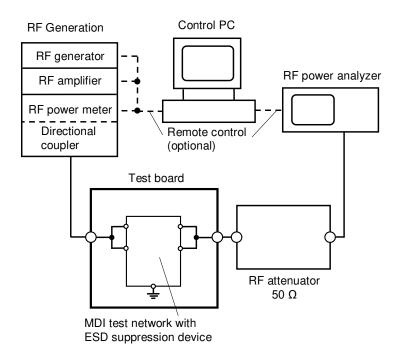

The test setup for measuring the unwanted clamping effect of ESD suppression device at RF immunity tests of a RF generation unit, consisting of RF generator, RF amplifier, RF power meter with directional coupler, in combination with a special test board, RF attenuator and RF power analyzer. The test setup is given in Figure 5-11.

Figure 5-11: Test setup for RF clamping test at ESD suppression device

The test equipment definitions are the following:

- RF generator;

- − RF amplifier (output impedance 50 Ω,  $P_{CW} \ge 10$  W);

- RF power meter with directional coupler;

- test board;

- − RF attenuator (impedance 50 Ω,  $P_{CW} \ge 10$  W,  $\ge 40$  dB attenuation), and

- control PC (optional).

An example for RF clamping test board is given in Figure 5-12.

Aug-23

Figure 5-12: Example of RF clamping test board for ESD suppression device, top layer

# 5.6.2 Test procedure and parameters

The required test procedure and parameters are defined in Table 5-14.

| Parameter                                       | Description                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                     |  |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| Frequency:                                      | Range                                                                                                                                                                                                                                                                                                                                                                  | Step                                                                                                                |  |

|                                                 | 1 MHz to 10 MHz                                                                                                                                                                                                                                                                                                                                                        | 0.25 MHz                                                                                                            |  |

|                                                 | 10 MHz to 100 MHz                                                                                                                                                                                                                                                                                                                                                      | 1 MHz                                                                                                               |  |

|                                                 | 100 MHz to 200 MHz                                                                                                                                                                                                                                                                                                                                                     | 2 MHz                                                                                                               |  |

|                                                 | 200 MHz to 400 MHz                                                                                                                                                                                                                                                                                                                                                     | 4 MHz                                                                                                               |  |

|                                                 | 400 MHz to 1000 MHz                                                                                                                                                                                                                                                                                                                                                    | 10 MHz                                                                                                              |  |

| Dwell time per step:                            | 1 s                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |  |

| Modulation:                                     | AM 80 % 1 kHz ( $\hat{P}_{\scriptscriptstyle AM}=\hat{P}_{\scriptscriptstyle CW}$ )                                                                                                                                                                                                                                                                                    |                                                                                                                     |  |

| Test parameter:                                 | CMR value                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                     |  |

| Test circuit:                                   | Note: The used CMC should fulfil the re                                                                                                                                                                                                                                                                                                                                | network  RF attenuator (50 $\Omega$ )  P_out  10BASE-T1S  equirements of [4].  ralue: CMR(f) = $P_in(f) - P_out(f)$ |  |

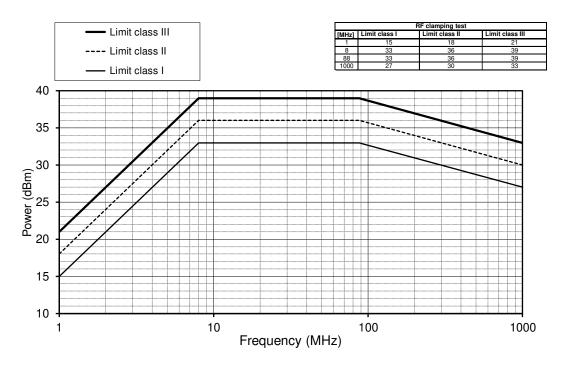

| Test power level:                               | Controlled forward power [dBm] for classes according to Figure 5-13                                                                                                                                                                                                                                                                                                    |                                                                                                                     |  |

| Test procedure:  Evaluation of clamping effect: | <ol> <li>test with test power 20 dBm for setting the reference value for CMR</li> <li>test with power level class I according Figure 5-13</li> <li>test with power level class II according to Figure 5-13</li> <li>test with power level class III according to Figure 5-13</li> <li>Maximum deviation of 1 dB from CMR reference value at 20 dBm for test</li> </ol> |                                                                                                                     |  |

|                                                 | power level according to limit classes                                                                                                                                                                                                                                                                                                                                 |                                                                                                                     |  |

Table 5-14: Test parameters for RF clamping test

Figure 5-13: Recommended test power levels for RF clamping tests at ESD suppression device

The tests should be performed at one sample and documented according to the scheme given in Table 5-15.

| Test  | Parameter | Sample   |  |

|-------|-----------|----------|--|

| RF-CL | CMR       | 1 sample |  |

Table 5-15: Required RF clamping test for ESD suppression device

The ESD suppression device should not show an unwanted clamping effect during the RF immunity test according to the evaluation criteria. Recommended limits are given in Annex A.5.