# Advanced diagnostic features for 100BASE-T1 automotive Ethernet PHYs

TC1 - advanced PHY features

| Author & Company  | Stefan Buntz (Daimler AG)                                 |

|-------------------|-----------------------------------------------------------|

| Title             | Advanced diagnostic features for automotive Ethernet PHYs |

| Version           | 1.0                                                       |

| Date              | July 4, 2017                                              |

| Status            | Final                                                     |

| Restriction Level | Public                                                    |

## **Version Control of Document**

| Version | Author       | Description   | Date         |

|---------|--------------|---------------|--------------|

| 1.0rc   | Stefan Buntz | First Version | 08 June 2017 |

|         |              |               |              |

# **Restriction level history of Document**

| Version | Restriction Level            | Description | Date         |

|---------|------------------------------|-------------|--------------|

| 1.0rc   | Confidential to OPEN members |             | 08 June 2017 |

| 1.0     | public                       |             | 04 July 2017 |

|         |                              |             |              |

|         |                              |             |              |

|         |                              |             |              |

|         |                              |             |              |

|         |                              |             |              |

|         |                              |             |              |

|         |                              |             |              |

|         |                              |             |              |

|         |                              |             |              |

|         |                              |             |              |

# **Contents**

| 1 | Disclai | imer                                             | 4  |

|---|---------|--------------------------------------------------|----|

| 2 | Introd  | luction                                          | 5  |

| 3 | Norma   | ative references                                 | 5  |

| 4 | Abbre   | viation                                          | 5  |

| 5 | Overv   | iew                                              | 6  |

| 6 | Advan   | nced PHY features                                | 7  |

|   | 6.1 D   | Dynamic Channel Quality (DCQ)                    | 7  |

|   | 6.1.1   | Mean Square Error (MSE)                          | 7  |

|   | 6.1.2   | Signal Quality Index (SQI)                       | 9  |

|   | 6.1.3   | Peak MSE value (pMSE)                            | 11 |

|   | 6.2 H   | Harness Defect Detection (HDD)                   | 12 |

|   | 6.2.1   | OPEN and SHORT detection (OS)                    | 12 |

|   | 6.3 L   | ink quality – start-up time and link losses (LQ) | 13 |

|   | 6.3.1   | Link training time (LTT)                         | 13 |

|   | 6.3.2   | Local receiver time (LRT)                        | 16 |

|   | 6.3.3   | Remote receiver time (RRT)                       | 17 |

|   | 6.3.4   | Link Failures and Losses (LFL)                   | 18 |

|   | 6.3.5   | Communication ready status (COM)                 | 19 |

|   | 6.4 P   | Polarity Detection and Correction (POL)          | 19 |

|   | 6.4.1   | Polarity Detection (DET)                         | 19 |

|   | 6.4.2   | Polarity Correction (COR)                        | 19 |

|   |         |                                                  |    |

## 1 Disclaimer

NOTICE TO USERS WHO ARE OPEN ALLIANCE SIG MEMBERS: Members of OPEN Alliance have the right to use and implement this Specification, subject to the Member's continued compliance with the OPEN Alliance SIG's governance documents, Intellectual Property Rights Policy, and the applicable OPEN Alliance Promoter or Adopters Agreement. OPEN Specification documents may only be reproduced in electronic or paper form or utilized in order to achieve the Scope, as defined in the OPEN Alliance Intellectual Property Rights Policy. Reproduction or utilization for any other purposes as well as any modification of the Specification document, in any form or by any means, electronic or mechanical, including photocopying and microfilm, is explicitly excluded.

NOTICE TO NON-MEMBERS OF OPEN ALLIANCE SIG: If you are not a Member of OPEN Alliance and you have obtained a copy of this document, you only have a right to review this document for informational purposes. You do not have the right to reproduce, distribute, make derivative works of, publicly perform or publicly display this document in any way.

All OPEN Specifications are provided on an "as is" basis and all warranties, either explicit or implied, are excluded unless mandatory under law. Accordingly, the OPEN Alliance Members who have contributed to the OPEN Specifications make no representations or warranties with regard to the OPEN Specifications or the information (including any software) contained therein, including any warranties of merchantability, fitness for purpose, or absence of third party rights and make no representations as to the accuracy or completeness of the OPEN Specifications or any information contained therein.

The OPEN Alliance Members who have contributed to the OPEN Specifications will not be liable for any losses, costs, expenses or damages arising in any way out of use or reliance upon any OPEN Specification or any information therein. Nothing in this document operates to limit or exclude any liability for fraud or any other liability which is not permitted to be excluded or limited by operation of law.

The material contained in OPEN Specifications is protected by copyright and may be subject to other types of Intellectual Property Rights.

The distribution of OPEN Specifications shall not operate as an assignment or license to any recipient of any OPEN Specification of any patents, registered designs, unregistered designs, trademarks, trade names or other rights as may subsist in or be contained in or reproduced in any OPEN Specification. The commercial exploitation of the material in this document may require such a license, and any and all liability arising out of use without such a license is excluded.

Without prejudice to the foregoing, the OPEN Alliance Specifications have been developed for automotive applications only. They have neither been developed, nor tested for non-automotive applications.

OPEN Alliance reserves the right to withdraw, modify, or replace any OPEN Specification at any time, without notice.

## 2 Introduction

This specification describes advanced features of an 100BASE-T1 automotive Ethernet PHY (often also called transceiver), e.g. for diagnostic purposes for automotive Ethernet PHYs.

## 3 Normative references

[1] IEEE P802.3bw<sup>™</sup> Physical Layer Specifications and Management Parameters for 100 Mb/s Operation over a Single Balanced Twisted Pair Cable (100BASE-T1)

## 4 Abbreviation

**RS-FEC** Reed Solomon Forward Error Correction

PHY is a Physical layer interface device, often called transceiver

ECU electronic control unit

DCQ dynamic channel quality

HDD Harness defect detection

LP Link Partner

LQ Link Quality

POL Polarity

MSE Mean Square Error

MSE\_WC Mean Square Error\_Worst Case

**SQI** Signal Quality Index

pMSE peak MSE

PEC Pulse Error Correction

OS OPEN/SHORT detection

DD Defect distance

LTT Link-training time

LRT Local Receiver Time

RRT Remote Receiver Time

LFL Link Failures and Losses

**COM** Communication ready (status bit)

DET Polarity detect

COR Polarity correct

## 5 Overview

100BASE-T1 automotive Ethernet transceivers (PHY or every PHY port of a switch) shall offer the information specified below for diagnostic purposes.

| group | group name                    | parameter | parameter<br>name           | Description                                                                                               | mandatory<br>/optional | remarks |

|-------|-------------------------------|-----------|-----------------------------|-----------------------------------------------------------------------------------------------------------|------------------------|---------|

| DCQ   | dynamic channel               | MSE       | Mean Square<br>Error        | The MSE (Mean Square Error) value of<br>the symbol detection shall be determined<br>in a standardized way | 0                      | 1)      |

|       |                               | SQI       | Signal Quality<br>Index     | A classification of the signal quality in 8 stages (3 bit) shall be carried out                           | m                      | 1), 2)  |

|       |                               | pMSE      | peak MSE                    | to identify short time noise (pulses) a<br>peak MSE value shall be provided (for<br>100BASE-T1)           | 0                      | 1)      |

| HDD   | Harness defect<br>detection   | OS        | OPEN/SHORT<br>detection     | Cable-Harness errors (short circuit or open line) shall be detected                                       | m                      |         |

| LQ    | LinkQuality                   | LTT       | Link-training time          | The time of the last link training shall be stored                                                        | m                      |         |

|       |                               | LRT       | Local Receiver<br>Time      | - The timing of the local receiver shall be stored                                                        | 0                      |         |

|       |                               | RRT       | Remote<br>Receiver Time     | - The timing of the remote receiver shall be stored                                                       | 0                      |         |

|       |                               | LFL       | Link Failures<br>and Losses | number of link losses since the last power cycle shall be stored                                          | m                      |         |

|       |                               | СОМ       | communication ready         | Optimized Link Status information. Signals when communication is possible.                                | m                      |         |

| POL   | Polarity detection&correction | DET       | Polarity detect             | according to the IEEE specifications of 100BASE-T1                                                        | m                      |         |

|       |                               | COR       | Polarity correct            | according to the IEEE specifications of 100BASE-T1                                                        | 0                      | 3)      |

Table 1: Overview of required PHY parameters to be stored and provided via registers.

#### Remarks to Table 1:

- 1) The dynamic channel quality shall be determined with a reasonable refresh rate and be stored in the corresponding defined registers. For the evaluation, of all registers that represent a dynamic signal quality, there shall be a second register providing the worst value since the last register reading process.

- 2) The 8 stages should correlate to according SNR values at the MDI and may represent corresponding bit error rates (in the case of an interference model with white noise).

- 3) In accordance with the specifications, polarity correction is optional in the case of 100BASE-T1.

All optional topics 'o' are initial proposals and are only seen as a rough framework. Optional features are not yet fully checked in terms or implementation, feasibility and thus could be changed or even dropped in a next version of this document.

## 6 Advanced PHY features

# 6.1 Dynamic Channel Quality (DCQ)

Dynamic channel quality includes MSE values, SQI values, and peak MSE values.

## 6.1.1 Mean Square Error (MSE)

#### Optional or mandatory feature: optional

Providing Mean Square Error information is optional. If provided, it is recommended to provide according to the described algorithm. The MSE information shall not be used for further qualification (e.g. for Interop Testing). For qualification purposes the mandatory SQI information is defined.

The PHY can provide a detailed information of the dynamic signal quality by means of a MSE value or comparable information. The MSE value can e.g. be determined from the MeanSquareError of the slicer. The following recommendations can be used as guidance for calculating and presenting the MSE value:

The MSE value should be determined with a refresh rate in the tolerance range of 0.8ms to 2.0ms. The following conventions for the determination of the MSE value can serve as a recommendation:

#### 100BASE-T1

The MSE value for 100BASE-T1 should be determined across 2^16 (65,536) symbols (summing up and normalization). With symbol duration of 15 ns this corresponds to a refresh rate of approx. 1.0ms. The resulting MSE value shall be linearly scaled to a value in the range of [0...511] and this value shall be placed in the register, DCQ.MSE.

In addition to the current MSE value the worst case MSE value since the last read should be stored in a second register.

| Register   | DCQ.MSE           |

|------------|-------------------|

| Name       | Mean Square Error |

| size[bits] | 9+1               |

| Bit   | Description                         |

|-------|-------------------------------------|

| [8:0] | MSE value                           |

| [9]   | MSE value valid [1=invalid;0=valid] |

| register value | Explanation |

|----------------|-------------|

| 0x0000         | MSE = 0     |

|                |             |

| 0x01FE         | MSE = 510   |

| 0x01FF         | MSE = 511   |

**Table 2 Definition of DCQ.MSE**

|           | D C C A A C E A A A C |  |

|-----------|-----------------------|--|

| Register  | DCQ.MSE_WC            |  |

| ricgister | DCQ.IVI3L_VVC         |  |

## **OPEN Alliance**

| Name       | Worst Case Mean Square Error |

|------------|------------------------------|

| size[bits] | 9+1                          |

| Bit   | description                         |

|-------|-------------------------------------|

| [8:0] | MSE value                           |

| [9]   | MSE value valid [1=invalid;0=valid] |

| register value | explanation |

|----------------|-------------|

| 0x0000         | MSE = 0     |

|                |             |

| 0x01FE         | MSE = 510   |

| 0x01FF         | MSE = 511   |

Table 3 Definition of DCQ.MSE\_WC

#### 6.1.2 Signal Quality Index (SQI)

## **Optional or mandatory feature: mandatory**

The signal quality value (SQI) shall be determined from the determined MSE value or comparable information. The SQI value shall be stored in a register in 8 levels (between "000" = worst value and "111" = 7 = best value).

In addition to the current SQI value, the lowest SQI value calculated since the last register read access shall be stored in the DCQ.SQI register as shown below.

| Register   | DCQ.SQI              |

|------------|----------------------|

| Name       | Signal Quality Index |

| size[bits] | 3                    |

| bit   | Description                          |

|-------|--------------------------------------|

| [0]   | Reserved                             |

| [3:1] | current SQI value                    |

| [4]   | Reserved                             |

| [7:5] | worst case SQI value since last read |

| register value | Explanation         |

|----------------|---------------------|

| 0x0            | SQI=0 (worst value) |

| 0x1            | SQI=1               |

| 0x2            | SQI=2               |

| 0x3            | SQI=3               |

| 0x4            | SQI=4               |

| 0x5            | SQI=5               |

| 0x6            | SQI=6               |

| 0x7            | SQI=7 (best value)  |

**Table 4 Definition of DCQ.SQI**

The following features of the SQI value are mandatory:

- Only for SQI=0 a link loss shall occur.

- The indicated signal quality shall monotonic increasing /decreasing with noise level.

- It shall be indicated in the datasheet at which level a BER<10^-10 (better than 10^-10) is achieved (e.g. "from SQI=3 to SQI=7 the link has a BER<10^-10 (better than 10^-10)")

During interoperability test the indicated signal quality shall be monitored and documented for information only.

#### **OPEN Alliance**

The recommended correlation between the SQI values stored in the register and an according signal to noise ratio (SNR) based on AWG noise (bandwidth of 80MHz) is shown in Table 5. The bit error rates to be expected in the case of white noise as interference signal is shown in the table as well for information purposes.

| SQI value | SNR value @MDI - AWG noise, 80MHz                         | recommended BER for AWG noise model |

|-----------|-----------------------------------------------------------|-------------------------------------|

|           | (informative)                                             | (informative)                       |

| SQI=0     | <18dB                                                     |                                     |

| SQI=1     | 18dB= <snr<19db< td=""><td>BER&gt;10^-10</td></snr<19db<> | BER>10^-10                          |

| SQI=2     | 19dB= <snr<20db< td=""><td></td></snr<20db<>              |                                     |

| SQI=3     | 20dB= <snr<21db< td=""><td></td></snr<21db<>              |                                     |

| SQI=4     | 21dB= <snr<22db< td=""><td></td></snr<22db<>              |                                     |

| SQI=5     | 22dB= <snr<23db< td=""><td>BER&lt;10^-10</td></snr<23db<> | BER<10^-10                          |

| SQI=6     | 23dB= <snr<24db< td=""><td></td></snr<24db<>              |                                     |

| SQI=7     | 24dB= <snr< td=""><td></td></snr<>                        |                                     |

Table 5 Recommended correlation from SQI to SNR under AWG assumption.

#### 6.1.3 Peak MSE value (pMSE)

#### Optional or mandatory feature: optional

Providing peakMSE information is optional. Goal of the peakMSE value is to identify transient disturbances which are typically in the μs-range. If this information is provided, it is recommended to provide according to the described algorithm. The peakMSE information shall not be used for further qualification (e.g. for Interop Testing). For qualification purposes the mandatory SQI information is defined.

For 100BASE-T1 a peakMSE value can be stored (identification of transient disturbances). The peakMSE value shall be determined from the MeanSquareError of the slicer. The value can be determined with a refresh rate in the tolerance range of 0.8ms to 2.0ms. The following conventions for the determination of the MSE value shall serve as a recommendation:

#### 100BASE-T1

The peakMSE value for 100BASE-T1 can be determined by a sliding window over 128 symbols. Each 2^16 (65,536) symbols the maximum value of this sliding window shall be stored in an 8bit register (range is 0...63). For symbol duration of 15ns the sliding window corresponds to a time of approx. 2.0µs. With symbol duration of 15 ns this corresponds to a refresh rate of approx. 1.0ms.

| Register   | DCQ.peakMSE (only 100BASE-T1) |

|------------|-------------------------------|

| Name       | peak MSE                      |

| size[bits] | 8 + 8                         |

| bit    | Description                               |

|--------|-------------------------------------------|

| [7:0]  | current peak MSE value                    |

| [15:8] | Worst case peak MSE value since last read |

| register value | explanation (100BASE-T1)                                       |

|----------------|----------------------------------------------------------------|

|                | for peakMSE (lower 8 bit) and worst case peakMSE (higher8 bit) |

| 0x00           | peakMSE = 0                                                    |

| 0x01           | peakMSE = 1                                                    |

|                |                                                                |

| 0x3E           | peakMSE = 62                                                   |

| 0xeF           | peakMSE = 63                                                   |

| 0x40 0xFE      | value invalid                                                  |

| 0xFF           | measurement not possible                                       |

Table 6 Definition of DCQ.peakMSE

# **6.2 Harness Defect Detection (HDD)**

#### 6.2.1 OPEN and SHORT detection (OS)

#### **Optional or mandatory feature: mandatory**

There shall be a possibility to detect harness defects. This can either be done during normal operation (as long as possible) or in a specific host-triggered diagnostic mode. With this functionality a PHY shall reliably detect the following error situations as long as the channel is properly terminated (link partner termination is connected to the channel):

- OPEN of one bus wire

- OPEN of both bus wires

- SHORT of both conductors (to ground or supply line)

- SHORT between both bus wires

- (OPTIONAL) SHORT of one conductor (to ground or supply line)\*

(OPEN = open circuit, SHORT = short circuit)

It is not needed to distinguish all of the above error situations individually.

#### Overview of failure types

Figure 1 Overview of error situations to be detected.

It is mandatory to detect all these failures when the LP is not transmitting any signal (typically "SEND\_Z" for 100BASE-T1 or as SLAVE). Optionally these failures are also detected when the LP is MASTER and transmitting e.g. TRAINING pattern.\*) REMARK: The condition of short circuit of one bus wire to GND or VBAT is not reliably detectable with today's technology. The detection of short circuit of one wire to GND or VBAT is therefore an optional feature. If no link loss is occurring, this only may be identified by higher layers due to significantly decreased signal quality. An indication for such a failure may be a significantly reduced SQI or sporadic link losses, which can be detected by higher layers (e.g. by SQI register or LinkLoss register).

Figure 2 Overview of error situation optionally to be detected.

Figure 3 is showing the Bus Failure Matrix, indicating which combinations of failures and environmental conditions are mandatory to detect and which combinations are optional.

| Bus Failure Matrix               | LP is SLAVE | LP is MASTER |

|----------------------------------|-------------|--------------|

| cable OK                         | mandatory   | optional     |

| Both bus wires OPEN              | mandatory   | optional     |

| Bus wires SHORT                  | mandatory   | optional     |

| One bus wire OPEN                | mandatory   | optional     |

| both bus wires SHORT to GND/VBAT | mandatory   | optional     |

| one bus wires SHORT to GND/VBAT  | optional    | optional     |

Figure 3 bus failure matrix.

# 6.3 Link quality - start-up time and link losses (LQ)

## 6.3.1 Link training time (LTT)

## **Optional or mandatory feature: mandatory**

The transceiver shall provide the time required to establish a link, in this context, the following time definitions apply:

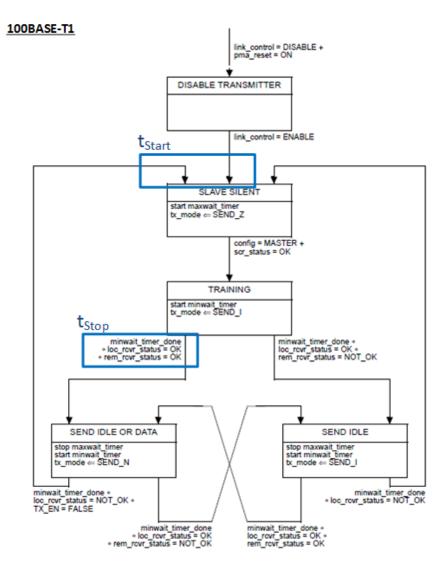

#### 100BASE-T1

```

Linkup\ Time\ (LU) = t_{Stop} - t_{Start}

t<sub>Start</sub> = time (link_control=ENABLE) OR

t<sub>Stop</sub>= time (loc_rcvr_status=OK & rem_rcvr_status=OK)

```

The timer for the time measurement shall be started when entering SLAVE SILENT, either from DISABLE\_TRANSMITTER or from a stable link (SEND\_IDLE\_OR\_DATA). The timer shall stop when entering SEND\_IDLE\_OR\_DATA (link has established).

The respective value for the start-up [in ms] shall be stored in an 8 bit register. Here, the value ranges from [0x00 = 0ms] to [0xFA = 250ms], all higher values shall be stored with [0xFB].

Figure 96-18-PHY Control state diagram

Figure 4 Definition of the start and end times for a determination of the start-up times of a 100BASE-T1 link.

| Register   | LQ.LTT             |

|------------|--------------------|

| Name       | Link-training time |

| size[bits] | 8                  |

| Bit   | description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| [7:0] | Information about the link training time of the last link training (lcl_rcv AND rem_rcv) |

| register value | explanation |

|----------------|-------------|

| 0x00           | 0ms         |

## **OPEN Alliance**

| 0x01 | 1ms                      |

|------|--------------------------|

|      |                          |

| 0x64 | 100ms                    |

|      |                          |

| 0xFA | 250ms                    |

| 0xFB | more than 250ms          |

|      | n/a                      |

| 0xFF | measurement not possible |

**Table 7 Definition of LQ.LTT**

## 6.3.2 Local receiver time (LRT)

## **Optional or mandatory feature: optional**

The transceiver shall provide the time required until the local receiver is locked, in this context, the following time definitions apply (t<sub>Start</sub> as in subclause 6.3.1):

## 100BASE-T1 Local Receiver Time (LRT) = time (loc\_rcvr\_status=OK) - t<sub>Start</sub>

| Register   | LQ.LRT              |

|------------|---------------------|

| Name       | Local Receiver Time |

| size[bits] | 8                   |

| Bit   | description                    |

|-------|--------------------------------|

| [7:0] | Time until local_receiver = OK |

| register value | explanation              |

|----------------|--------------------------|

| 0x00           | 0ms                      |

| 0x01           | 1ms                      |

|                |                          |

| 0x64           | 100ms                    |

|                |                          |

| 0xFA           | 250ms                    |

| 0xFB           | more than 250ms          |

|                | n/a                      |

| 0xFF           | measurement not possible |

**Table 8 Definition of LQ.LRT register**

## 6.3.3 Remote receiver time (RRT)

## **Optional or mandatory feature: optional**

The transceiver shall provide the time required until the remote receiver is signaling that he is locked, in this context, the following time definitions apply (t<sub>Start</sub> as in subclause 6.3.1):

#### 100BASE-T1

Remote Receiver Time (RRT) = time (rem\_rcvr\_status=OK) -t<sub>Start</sub>

| Register   | LQ.RRT               |

|------------|----------------------|

| Name       | Remote Receiver Time |

| size[bits] | 8                    |

| Bit   | description                     |

|-------|---------------------------------|

| [7:0] | Time until remote_receiver = OK |

| register value | explanation              |

|----------------|--------------------------|

| 0x00           | 0ms                      |

| 0x01           | 1ms                      |

|                |                          |

| 0x64           | 100ms                    |

|                |                          |

| 0xFA           | 250ms                    |

| 0xFB           | more than 250ms          |

|                | n/a                      |

| 0xFF           | measurement not possible |

**Table 9 Definition of LQ.RRT register**

## 6.3.4 Link Failures and Losses (LFL)

## **Optional or mandatory feature: mandatory**

The PHY shall store the number of failures which occurred since the last power cycle but did not cause a link loss in a 10bit register.

The PHY shall store the number of link losses which occurred since the last power cycle in a 6bit register.

| Register   | LQ.LFL                   |

|------------|--------------------------|

| Name       | Link Failures and Losses |

| size[bits] | 16                       |

| Bit     | description                                                                                                     |

|---------|-----------------------------------------------------------------------------------------------------------------|

| [9:0]   | Number of Link Failures causing NOT a link loss (SSD failure, ESD failure, etc.) since last power cycle (01023) |

| [15:10] | number of Link Losses occurred since last power cycle (063)                                                     |

| register [9:0] | explanation                   |

|----------------|-------------------------------|

| 0x000          | 0 failure                     |

| 0x001          | 1 failure                     |

|                |                               |

| 0x3FE          | 1022 failures                 |

| 0x3FF          | 1023 or more failures occured |

| register | explanation                    |

|----------|--------------------------------|

| [15:10]  |                                |

| 0x00     | 0 link losses occured          |

| 0x01     | 1 link loss occured            |

|          |                                |

| 0x3E     | 62 link losses occured         |

| 0x3F     | 63 or more link losses occured |

**Table 10 Definition of LQ.LFL register**

#### 6.3.5 Communication ready status (COM)

#### **Optional or mandatory feature: mandatory**

The Communication ready (Comm ready) status is an optimized Link Status information which shall be provided via the extended status register as information for higher layers to signal that from now on communication via the link is possible.

The optimized link status shall be defined by the status of the scrambler (scr status), the local receiver status (loc\_rcvr\_status) and the remote receiver status (rem\_rcvr\_status) together with a hysteresis of 2ms in case of switching from NOT OK to OK status (if all status information are OK).

#### 100BASE-T1

Comm\_ready = (loc\_rcvr\_status & rem\_rcvr\_status & scr\_status); hysteresis 2ms

| Register   | LQ.COM                     |

|------------|----------------------------|

| Name       | Communication Ready Status |

| size[bits] | 1                          |

| bit | Description                        |

|-----|------------------------------------|

| [0] | information on communication_ready |

| register [0] | Explanation                        |

|--------------|------------------------------------|

| 0            | Communication_ready = NOT OK/FALSE |

| 1            | Communication_ready = OK/TRUE      |

**Table 11 Definition of LQ.COM**

# 6.4 Polarity Detection and Correction (POL)

#### 6.4.1 Polarity Detection (DET)

#### **Optional or mandatory feature: mandatory**

Polarity detection, as well as their diagnostic accessibility (registers) shall be implemented in accordance with the specifications (100BASE-T1).

## 6.4.2 Polarity Correction (COR)

## Optional or mandatory feature: 100BASE-T1 optional

Polarity correction, as well as their diagnostic accessibility (registers) shall be implemented in accordance with the specifications (100BASE-T1). If polarity correction is implemented it shall be possible to disable this feature.