# Advanced diagnostic features for 1000BASE-T1 automotive Ethernet PHYs

TC12 - Advanced PHY features

| Author & Company  | Michael Kaindl, BMW                                       |

|-------------------|-----------------------------------------------------------|

| Title             | Advanced diagnostic features for automotive Ethernet PHYs |

| Version           | 2.2                                                       |

| Date              | December 4, 2024                                          |

| Status            | Final                                                     |

| Restriction Level | Public                                                    |

© 2024 OPEN Alliance. This document also contains contents, the copyrights of which are owned by third parties who are OPEN Alliance Contributing Members. Unauthorized Use Strictly Prohibited. All Rights Reserved.

# Contents

| 1 | OPEN  | VAlliance Specification Copyright Notice and Disclaimer                | 3  |

|---|-------|------------------------------------------------------------------------|----|

|   | 1.1   | OPEN Specification Ownership and Usage Rights                          | 3  |

|   | 1.2   | Rights and Usage Restrictions Specific to OPEN Alliance Members        | 3  |

|   | 1.2.1 | Rights and Usage Restrictions Specific to Non-members of OPEN Alliance | 3  |

|   | 1.3   | Terms Applicable to both Members and Non-members of OPEN Alliance      | 4  |

|   | 1.3.1 | Patents, Trademarks, and other Rights:                                 | 4  |

|   | 1.3.2 | Disclaimers and Limitations of Liability:                              | 4  |

|   | 1.3.3 | Compliance with Laws and Regulations:                                  | 4  |

|   | 1.3.4 | Automotive Applications Only:                                          | 5  |

|   | 1.3.5 | Right to Withdraw or Modify:                                           | 5  |

| 2 | Intro | duction                                                                | 6  |

| 3 | Norm  | native references                                                      | 6  |

| 4 | Abbr  | eviation/Symbols                                                       | 6  |

| 5 | Over  | view                                                                   | 7  |

|   | 5.1   | Register Size and Register Definitions                                 | 8  |

|   | 5.2   | Clear/Reset Register                                                   | 8  |

| 6 | Adva  | nced PHY features                                                      | 9  |

|   | 6.1   | Dynamic Channel Quality (DCQ)                                          | 9  |

|   | 6.1.1 | Mean Square Error (MSE)                                                | 9  |

|   | 6.1.2 | Signal Quality Index (SQI)                                             | 9  |

|   | 6.2   | Harness Defect Detection (HDD)                                         | 11 |

|   | 6.2.1 | OPEN and SHORT detection (OS)                                          | 11 |

|   | 6.2.2 | Time Delay Reflection (TDR)                                            | 12 |

|   | 6.3   | Link quality – start-up time and link losses (LQ)                      | 13 |

|   | 6.3.1 | Linkup Total Time (LTT)                                                | 13 |

|   | 6.3.2 | Local receiver time (LRT)                                              | 16 |

|   | 6.3.3 | Remote receiver time (RRT)                                             | 18 |

|   | 6.3.4 | Link Losses (LL)                                                       | 18 |

|   | 6.3.5 | Communication ready status (COM)                                       | 18 |

|   | 6.4   | Polarity Detection and Correction (POL)                                | 19 |

|   | 6.5   | Forward Error Correction Counter                                       | 19 |

|   | 6.5.1 | FEC Counter (FECC)                                                     | 19 |

# **1** OPEN Alliance Specification Copyright Notice and Disclaimer

# 1.1 OPEN Specification Ownership and Usage Rights

As between OPEN Alliance and OPEN Alliance Members whose contributions were incorporated in this OPEN Specification (the "Contributing Members"), the Contributing Members own the worldwide copyrights in and to their given contributions. Other than the Contributing Members' contributions, OPEN Alliance owns the worldwide copyrights in and to compilation of those contributions forming this OPEN Specification. For OPEN Alliance Members (as that term is defined in the OPEN Alliance Bylaws), OPEN Alliance permits the use of this OPEN Specification on the terms in the OPEN Alliance Intellectual Property Rights Policy and the additional applicable terms below. For non-members of OPEN Alliance, OPEN Alliance permits the use of this OPEN Specification on the terms in the OPEN Alliance, Agreement (available here: http://www.opensig.org/Automotive-Ethernet-Specifications/) and the additional applicable terms below. The usage permissions referenced and described here relate only to this OPEN Specification. By using this OPEN Specification, you hereby agree to the following terms and usage restrictions:

# 1.2 Rights and Usage Restrictions Specific to OPEN Alliance Members

FOR OPEN ALLIANCE MEMBERS ONLY: In addition to the usage terms and restrictions granted to Members in the OPEN Alliance Intellectual Property Rights Policy, Members' use of this OPEN Specification is subject this Copyright Notice and Disclaimer. Members of OPEN Alliance have the right to use this OPEN Specification solely (i) during the term of a Member's membership in OPEN Alliance and subject to the Member's continued membership in good standing in OPEN Alliance; (ii) subject to the Member's continued compliance with the OPEN Alliance governance documents, Intellectual Property Rights Policy, and the applicable OPEN Alliance Promoter or Adopter Agreement, as applicable; and (iii) for internal business purposes and solely to use the OPEN Specification for implementation of this OPEN Specification in the Member's products and services, but only so long as Member does not distribute, publish, display, or transfer this OPEN Specification to any third party, except as expressly set forth in Section 11 of the OPEN Alliance Intellectual Property Rights Policy. Except and only to the extent required to use this OPEN Specification internally for implementation of this OPEN Specification in Member's products and services, Member shall not modify, alter, combine, delete portions of, prepare derivative works of, or create derivative works based upon this OPEN Specification. If Member creates any modifications, alterations, or other derivative works of this OPEN Specification as permitted to use the same internally for implementation of this OPEN Specification in Member's products and services, all such modifications, alterations, or other derivative works shall be deemed part of, and licensed to such Member under the same restrictions as, this OPEN Specification. For the avoidance of doubt, Member shall not include all or any portion of this OPEN Specification in any other technical specification or technical material, product manual, marketing material, or any other material without OPEN Alliance's prior written consent. All rights not expressly granted to Member in the OPEN Alliance Intellectual Property Rights Policy are reserved.

#### 1.2.1 Rights and Usage Restrictions Specific to Non-members of OPEN Alliance

FOR NON-MEMBERS OF OPEN ALLIANCE ONLY: Use of this OPEN Specification by anyone who is not a Member in good standing of OPEN Alliance is subject to your agreement to the OPEN Alliance Specification License Agreement (available here: <a href="http://www.opensig.org/Automotive-Ethernet-Specifications/">http://www.opensig.org/Automotive-Ethernet-Specifications/</a> ) and the additional terms in this Copyright Notice and Disclaimer. Non-members have the right to use this OPEN Specification solely (i) subject to the non-member's continued compliance with the OPEN Alliance Specification License Agreement; and (ii) for internal business purposes and solely to use the OPEN Specification for implementation of this OPEN Specification in the non-member's products and services, but only so long as non-member does not distribute, publish, display, or transfer this OPEN Specification to any third party, unless and only to the extent expressly set forth in the OPEN Alliance Specification License Agreement. Except and only to the extent required to use this OPEN Specification internally for implementation of this OPEN Specification in non-member's products and services, non-member shall

© 2024 OPEN Alliance Dec-24 3 not modify, alter, combine, delete portions of, prepare derivative works of, or create derivative works based upon this OPEN Specification. If non-member creates any modifications, alterations, or other derivative works of this OPEN Specification as permitted to use the same internally for implementation of this OPEN Specification in non-member's products and services, all such modifications, alterations, or other derivative works shall be deemed part of, and licensed to such non-member under the same restrictions as, this OPEN Specification. For the avoidance of doubt, non-member shall not include all or any portion of this OPEN Specification in any other technical specification or technical material, product manual, marketing material, or any other material without OPEN Alliance's prior written consent. All rights not expressly granted to non-member in the OPEN Alliance Specification License Agreement are reserved.

## 1.3 Terms Applicable to both Members and Non-members of OPEN Alliance

#### **1.3.1** Patents, Trademarks, and other Rights:

OPEN Alliance has received no Patent Disclosure and Licensing Statements related to this OPEN Specification. Therefore, this OPEN Specification contains no specific disclaimer related to third parties that may require a patent license for their Essential Claims. Having said that, the receipt of this OPEN Specification shall not operate as an assignment of or license under any patent, industrial design, trademark, or other rights as may subsist in or be contained in or reproduced in this OPEN Specification; and the implementation of this OPEN Specification could require such a patent license from a third party. You may not use any OPEN Alliance trademarks or logos without OPEN Alliance's prior written consent.

#### **1.3.2 Disclaimers and Limitations of Liability:**

THIS OPEN SPECIFICATION IS PROVIDED ON AN "AS IS" BASIS, AND ALL REPRESENTATIONS, WARRANTIES, AND GUARANTEES, EITHER EXPLICIT, IMPLIED, STATUTORY, OR OTHERWISE, ARE EXCLUDED AND DISCLAIMED UNLESS (AND THEN ONLY TO THE EXTENT THEY ARE) MANDATORY UNDER LAW. ACCORDINGLY, OPEN ALLIANCE AND THE CONTRIBUTING MEMBERS MAKE NO REPRESENTATIONS OR WARRANTIES OR GUARANTEES WITH REGARD TO THIS OPEN SPECIFICATION OR THE INFORMATION (INCLUDING ANY SOFTWARE) CONTAINED HEREIN. OPEN ALLIANCE AND ALL CONTRIBUTING MEMBERS HEREBY EXPRESSLY DISCLAIM ANY AND ALL SUCH EXPRESS, IMPLIED, STATUTORY, AND ALL OTHER REPRESENTATIONS, WARRANTIES, AND GUARANTEES, INCLUDING WITHOUT LIMITATION ANY AND ALL WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR USE, TITLE, NON-INFRINGEMENT OF OR ABSENCE OF THIRD PARTY RIGHTS, AND/OR VALIDITY OF RIGHTS IN THIS OPEN SPECIFICATION; AND OPEN ALLIANCE AND THE CONTRIBUTING MEMBERS MAKE NO REPRESENTATIONS AS TO THE ACCURACY OR COMPLETENESS OF THIS OPEN SPECIFICATION OR ANY INFORMATION CONTAINED HEREIN. WITHOUT LIMITING THE FOREGOING, OPEN ALLIANCE AND/OR CONTRIBUTING MEMBERS HAS(VE) NO OBLIGATION WHATSOEVER TO INDEMNIFY OR DEFEND YOU AGAINST CLAIMS RELATED TO INFRINGEMENT OR MISAPPROPRIATION OF INTELLECTUAL PROPERTY RIGHTS.

OPEN ALLIANCE AND CONTRIBUTING MEMBERS ARE NOT, AND SHALL NOT BE, LIABLE FOR ANY LOSSES, COSTS, EXPENSES, OR DAMAGES OF ANY KIND WHATSOEVER (INCLUDING WITHOUT LIMITATION DIRECT, INDIRECT, SPECIAL, INCIDENTAL, CONSEQUENTIAL, PUNITIVE, AND/OR EXEMPLARY DAMAGES) ARISING IN ANY WAY OUT OF USE OR RELIANCE UPON THIS OPEN SPECIFICATION OR ANY INFORMATION HEREIN. NOTHING IN THIS DOCUMENT OPERATES TO LIMIT OR EXCLUDE ANY LIABILITY FOR FRAUD OR ANY OTHER LIABILITY WHICH IS NOT PERMITTED TO BE EXCLUDED OR LIMITED BY OPERATION OF LAW.

#### **1.3.3 Compliance with Laws and Regulations:**

NOTHING IN THIS DOCUMENT OBLIGATES OPEN ALLIANCE OR CONTRIBUTING MEMBERS TO PROVIDE YOU WITH SUPPORT FOR, OR RELATED TO, THIS OPEN SPECIFICATION OR ANY IMPLEMENTED PRODUCTS OR SERVICES. NOTHING IN THIS OPEN SPECIFICATION CREATES ANY WARRANTIES OR GUARANTEES, EITHER EXPRESS OR IMPLIED, STATUTORY OR OTHERWISE, REGARDING ANY LAW OR REGULATION. OPEN ALLIANCE AND CONTRIBUTING MEMBERS EXPRESSLY DISCLAIM ALL LIABILITY, INCLUDING WITHOUT LIMITATION, LIABILITY FOR NONCOMPLIANCE WITH LAWS, RELATING TO USE OF THE OPEN SPECIFICATION OR INFORMATION CONTAINED HEREIN. YOU ARE SOLELY RESPONSIBLE FOR THE COMPLIANCE OF IMPLEMENTED PRODUCTS AND SERVICES WITH ANY SUCH LAWS AND REGULATIONS, AND FOR OBTAINING ANY AND ALL REQUIRED AUTHORIZATIONS, PERMITS, AND/OR LICENSES FOR IMPLEMENTED PRODUCTS AND SERVICES RELATED TO SUCH LAWS AND REGULATIONS WITHIN THE APPLICABLE JURISDICTIONS.

IF YOU INTEND TO USE THIS OPEN SPECIFICATION, YOU SHOULD CONSULT ALL APPLICABLE LAWS AND REGULATIONS. COMPLIANCE WITH THE PROVISIONS OF THIS OPEN SPECIFICATION DOES NOT CONSTITUTE COMPLIANCE TO ANY APPLICABLE LEGAL OR REGULATORY REQUIREMENTS. IMPLEMENTERS OF THIS OPEN SPECIFICATION ARE SOLELY RESPONSIBLE FOR OBSERVING AND COMPLYING WITH THE APPLICABLE LEGAL AND REGULATORY REQUIREMENTS. WITHOUT LIMITING THE FOREGOING, YOU SHALL NOT USE, RELEASE, TRANSFER, IMPORT, EXPORT, AND/OR RE-EXPORT THIS OPEN SPECIFICATION OR ANY INFORMATION CONTAINED HEREIN IN ANY MANNER PROHIBITED UNDER ANY APPLICABLE LAWS AND/OR REGULATIONS, INCLUDING WITHOUT LIMITATION U.S. EXPORT CONTROL LAWS.

#### **1.3.4** Automotive Applications Only:

Without limiting the foregoing disclaimers or limitations of liability in any way, this OPEN Specification was developed for automotive applications only. This OPEN Specification has neither been developed, nor tested for, non-automotive applications.

#### **1.3.5** Right to Withdraw or Modify:

OPEN Alliance reserves the right to (but is not obligated to) withdraw, modify, or replace this OPEN Specification at any time, without notice.

© 2024 OPEN Alliance. This document also contains contents, the copyrights of which are owned by third parties who are OPEN Alliance Contributing Members. Unauthorized Use Strictly Prohibited. All Rights Reserved.

# 2 Introduction

This specification describes advanced features of a 1000BASE-T1 automotive Ethernet PHY (often also called transceiver), e.g. for diagnostic purposes for automotive Ethernet PHYs.

# **3** Normative references

[1] IEEE P802.3bp<sup>™</sup> Amendment 4: Physical Layer Specifications and Management Parameters for 1 Gb/s Operation over a Single Twisted-Pair Copper Cable - Clause 97

# 4 Abbreviation/Symbols

| ! NOT<br>+ OR                                                      |     |

|--------------------------------------------------------------------|-----|

| -                                                                  |     |

|                                                                    |     |

| COM Communication ready (status bit)                               |     |

| DCQ Dynamic Channel Quality                                        |     |

| DD Defect distance                                                 |     |

| ECU Electronic Control Unit                                        |     |

| FEC Forward Error Correction                                       |     |

| FECC FEC Event Counter                                             |     |

| HDD Harness defect detection                                       |     |

| LL Link Losses                                                     |     |

| LP Link Partner                                                    |     |

| LQ Link Quality                                                    |     |

| LRT Local Receiver Time                                            |     |

| LTT LinkUp Total Time                                              |     |

| MSE Mean Square Error                                              |     |

| MSE_WC Mean Square Error Worst Case                                |     |

| OS OPEN/SHORT detection                                            |     |

| PHY PHY is a Physical layer interface device, often called transce | ver |

| POL Polarity detection and correction                              |     |

| RRT Remote Receiver Time                                           |     |

| SQI Signal Quality Index                                           |     |

| TDR Time Delay Reflectometry                                       |     |

# **5 Overview**

1000BASE-T1 automotive Ethernet transceivers (PHY or every PHY port of a switch) shall offer the information specified below for diagnostic purposes.

| group | group name                         | parameter | parameter<br>name                               | description                                                                                               | mandatory<br>/optional | remarks |

|-------|------------------------------------|-----------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------|---------|

| DCQ   | Dynamic Channel<br>Quality         | MSE       | Mean Square<br>Error                            | The MSE (Mean Square Error) value of<br>the symbol detection shall be determined<br>in a standardized way | 0                      | 1)      |

|       |                                    | SQI       | Signal Quality<br>Index                         | A classification of the signal quality in 8 stages (3 bit) shall be carried out                           | m                      | 1), 2)  |

| HDD   | Harness defect detection           | OS        | OPEN/SHORT<br>detection                         | Cable harness errors (short circuit or open line) shall be detected                                       | m                      |         |

|       | TDR based Cable                    | TDR       | SHORT/OPEN/N<br>OISE /<br>DISTANCE<br>detection | Cable harness errors detected by TDR-<br>like test approach                                               | m                      |         |

| LQ    | Link Quality                       | LTT       | LinkUp Total<br>Time                            | The time of the last link training shall be stored                                                        | m                      |         |

|       |                                    | LRT       | Local Receiver<br>Time                          | The timing of the local receiver shall be stored                                                          | 0                      |         |

|       |                                    | RRT       | Remote<br>Receiver Time                         | The timing of the remote receiver shall be stored                                                         | 0                      |         |

|       |                                    | LL        | Link Losses                                     | number of link losses since the last power cycle shall be stored                                          | m                      |         |

|       |                                    | СОМ       | communication<br>ready                          | Optimized Link Status information.<br>Signals when communication is possible.                             | m                      |         |

| POL   | Polarity detection &<br>correction | POL       |                                                 |                                                                                                           |                        |         |

| FEC   | Forward Error<br>Correction        | FECC      | FEC Counter                                     | FEC counter                                                                                               | m                      |         |

Table 1: Overview of required PHY parameters.

Remarks to Table 1:

1) The dynamic channel quality shall be determined with a reasonable refresh rate and be stored in the corresponding defined registers. For the evaluation of all registers that represent a dynamic signal quality, there shall be a second register providing the worst value since the last register reading process.

2) The 8 stages shall correlate to the SNR values at the MDI and may represent corresponding bit error rates (in the case of an interference model with white noise).

All optional topics 'o' are initial proposals and are only seen as a rough framework. Optional features are not yet fully checked in terms of implementation or feasibility and thus could be changed or even dropped in a future version of this document.

**Bold**: Features for plant, maintenance and service: Standardized access is required

# 5.1 Register Size and Register Definitions

IEEE defines for the MDIO Access a standard register size of 16Bit. In order to get an effective register access, registers may contain a group of information when the data are related to the same subject and will be used potentially within the same software entity.

The term register within this document may comprise the access to a single data register in a most basic form as well as the procedural access to a group of single bit and registers or an implemented functional feature of the Ethernet PHY, which process the according data.

The organisation and implementation of registers is vendor specific.

# 5.2 Clear/Reset Register

All register are set to their default values after Power on Reset and HW Reset. For register within the advanced diagnostic features the SW reset shall be equivalent to a HW-Reset

# 6 Advanced PHY features

# 6.1 Dynamic Channel Quality (DCQ)

Dynamic channel quality includes MSE values and SQI values.

## 6.1.1 Mean Square Error (MSE)

#### **Optional or mandatory feature: Optional**

Providing Mean Square Error information is optional, if provided it is recommended that the calculation is defined and controlled by the implementer. The MSE information shall not be used for further qualification (e.g. for Interop Testing). For qualification purposes the mandatory SQI information is defined.

The PHY can provide detailed information of the dynamic signal quality by means of a MSE value or comparable information. The MSE value can be determined from the MeanSquareError of the slicer.

The implementation is vendor specific.

The following recommendations can be used as guidance for calculating and presenting the MSE value:

The MSE value for 1000BASE-T1 should be determined across 2^16 (65,536) symbols (summing up and normalization), with a refresh rate in the tolerance range of 80us – 200us. The resulting MSE value shall be linearly scaled to a value in the range of [0...511] and this value shall be placed in the register, DCQ.MSE.

In addition to the current MSE value, the worst case MSE value since the last read should be stored in a second register.

|             | DCQ.MSE                   |

|-------------|---------------------------|

| Name        | Mean Square Error         |

| Description | MSE value Vendor specific |

Table 2 Definition of DCQ.MSE

|             | DCQ.MSE_WC                       |

|-------------|----------------------------------|

| Name        | Worst Case Mean Square Error     |

| Description | Max MSE value ; Vendors Specific |

Table 3 Definition of DCQ.MSE\_WC

## 6.1.2 Signal Quality Index (SQI)

#### **Optional or mandatory feature: mandatory**

The signal quality value (SQI) shall be determined from the determined MSE value or comparable information. The SQI value shall be stored in a register in 8 levels (between "000" = worst value and "111" = 7 = best value).

In addition to the current SQI value, the lowest SQI value calculated since the last register read access shall be stored in the DCQ.SQI register as shown below.

|                       | DCQ.SQI                              |

|-----------------------|--------------------------------------|

| Name                  | Signal Quality Index                 |

| Description           | current SQI value                    |

| Description           | worst case SQI value since last read |

| Table 4 Definition of | DCO-SQI                              |

Table 4 Definition of DCQ.SQI

The following features of the SQI value are mandatory:

- When the register value outputs a value of 0 a link loss shall be recorded through the LQ.LFL register.

- The indicated signal quality shall monotonically increase /decrease with noise level.

- It shall be indicated in the datasheet at which level a BER<10^-10 (better than 10^-10) is achieved (e.g. "from SQI=3 to SQI=7 the link has a BER<10^-10 (better than 10^-10)")

During interoperability testing the indicated signal quality shall be monitored and documented for information only.

The recommended correlation between the SQI values stored in the register and an accompanying signal to noise ratio (SNR) based on AWG noise (bandwidth of 550MHz) is shown in Table 5. The bit error rates to be expected in the case of white noise as interference signal are shown in the table as well for information purposes.

| SQI value | SNR value @MDI - AWG noise, 550MHz<br>(informative)       | recommended BER for AWG noise model (informative) |

|-----------|-----------------------------------------------------------|---------------------------------------------------|

| SQI=0     | <18dB                                                     |                                                   |

| SQI=1     | 18dB= <snr<19db< td=""><td>BER&gt;10^-10</td></snr<19db<> | BER>10^-10                                        |

| SQI=2     | 19dB= <snr<20db< td=""><td></td></snr<20db<>              |                                                   |

| SQI=3     | 20dB= <snr<21db< td=""><td></td></snr<21db<>              |                                                   |

| SQI=4     | 21dB= <snr<22db< td=""><td></td></snr<22db<>              |                                                   |

| SQI=5     | 22dB= <snr<23db< td=""><td>BER&lt;10^-10</td></snr<23db<> | BER<10^-10                                        |

| SQI=6     | 23dB= <snr<24db< td=""><td></td></snr<24db<>              |                                                   |

| SQI=7     | 24dB= <snr< td=""><td></td></snr<>                        |                                                   |

Table 5 Recommended correlation from SQI to SNR under AWG assumption.

# 6.2 Harness Defect Detection (HDD)

## 6.2.1 OPEN and SHORT detection (OS)

## Optional or mandatory feature: Mandatory

There shall be a possibility to detect harness defects. This can either be done during normal operation (as long as possible) or after a failure event e.g. an established link is interrupted is signalled or in a specific host-triggered diagnostic mode. With this functionality a PHY shall reliably detect the following error situations as long as the channel is properly terminated (link partner termination is connected to the channel):

- OPEN of one bus wire

- OPEN of both bus wires

- SHORT of both conductors (to ground or supply line)

- SHORT between both bus wires

- (OPTIONAL) SHORT of one conductor (to ground or supply line)\*

(OPEN = open circuit, SHORT = short circuit)

It is not needed to distinguish all of the above error situations individually.

It is mandatory to detect all these failures when the LP is not transmitting any signal (typically "SEND\_Z" for 1000BASE-T1 or as SLAVE). Optionally these failures are also detected when the LP is MASTER and transmitting e.g. TRAINING pattern.\*) REMARK: The condition of short circuit of one bus wire to GND or VBAT is not reliably detectable with today's technology. The detection of short circuit of one wire to GND or VBAT is therefore an optional feature. If no link loss is occurring, this only may be identified by higher layers due to significantly decreased signal quality. An indication for such a failure may be a significantly reduced SQI or sporadic link losses, which can be detected by higher layers (e.g. by SQI register or Link Losses register).

one bus wire connected to GND or V<sub>bat</sub>

Figure 2 Overview of error situation optionally to be detected.

**Fehler! Verweisquelle konnte nicht gefunden werden.** Table 7 is showing the Bus Failure Matrix, indicating which combinations of failures and environmental conditions are mandatory to detect and which combinations are optional.

|             | HDD.OS                                                               |

|-------------|----------------------------------------------------------------------|

| Name        | OS                                                                   |

| Description | Cable OK                                                             |

|             | OPEN detect (one or both bus wires)                                  |

|             | SHORT detect (of bus wires; of one or both bus wires to GND or VBAT) |

Table 6 Open / Short detection

| Bus Failure Matrix              | LP is SLAVE | LP is MASTER |

|---------------------------------|-------------|--------------|

| cable OK                        | mandatory   | optional     |

| OPEN detect                     | mandatory   | optional     |

| SHORT detect                    | mandatory   | optional     |

| one bus wires SHORT to GND/VBAT | optional    | optional     |

Table 7 Bus failure matrix

## 6.2.2 Time Delay Reflection (TDR)

#### **Optional or mandatory feature: mandatory**

There shall be the possibility to use a TDR based diagnostic feature for cable diagnostic. This feature is applicable only in diagnostic mode of the PHY device and shall not be activated during normal operation. The TDR diagnostic feature shall be available in both PHY modes: Master or Slave. This diagnostic mode shall be available on a 1000BASE-T1 device independent if operating in 100BASE-T1 or 1000BASE-T1 mode.

Distances to fault above 15m are optional as the channel definition with the OpenAlliance is limited to 15m. The TDR results above the working area of the specific device, the result shall be indicated as "resolution not possible / out of distance"

Activating the TDR feature shall deliver the following information:

|             | HDD.TDR (only 1000BASE-T1 devices)                    |

|-------------|-------------------------------------------------------|

| Name        | TDR                                                   |

| Description | TDR activation                                        |

| Description | Short                                                 |

|             | Open                                                  |

|             | Noise                                                 |

|             | Cable O.K Test in progress; initial value with TDR ON |

|             | Test not possible (e.g. active link/communication)    |

|             |                                                       |

#### **OPEN** Alliance

| 1Bit = Distance to 1 <sup>st</sup> / main fault 1Bit approx. 1m<br>000000 = no error<br>000001 = error about 0-1m away<br>000010 = error between 1-2m away | approx. 1 31m |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| <br>011111= error about 30-31m away<br>111111 = resolution not possible / out of distance                                                                  |               |

Table 8 Definition of HDD.TDR

# 6.3 Link quality – start-up time and link losses (LQ)

## 6.3.1 Linkup Total Time (LTT)

## **Optional or mandatory feature: mandatory**

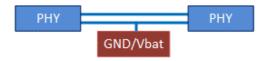

Figure 3 and Figure 4 Definition of the start and end times for a determination of the start-up times of a 1000BASE-T1 link.

The transceiver shall provide the time required from enabling the PHY to establish a link. In this context, the following time definitions apply:

1000BASE-T1

Linkup\_Total\_Time (LU) = t\_stop - t\_start

The Link Up Counter is an internal 11 bit counter; with an bit increment each 1ms.

- For Link Synchronization mode, the counter starts when the PHY transits from SYNC\_DISABLE state or LINK\_GOOD\_state.

- For AutoNegotiation mode, the counter starts when PHY transits from AutoNegotiation\_Enable state or AN\_GOOD state to TRANSMIT\_DISABLE state.

- Counter stops when the Link is Up (Link\_status\_changes fail to OK) and it will be reset to 0 after its value is recorded by the Linkup\_Total\_Time Register.

t\_start = Start of Linkup\_Total\_Time Counter -- Link Sync State Machine

Figure 3 Linkup\_Total\_Time Start and stop condition for timing measurement at 1000BASE-T1 with Link Synchronization

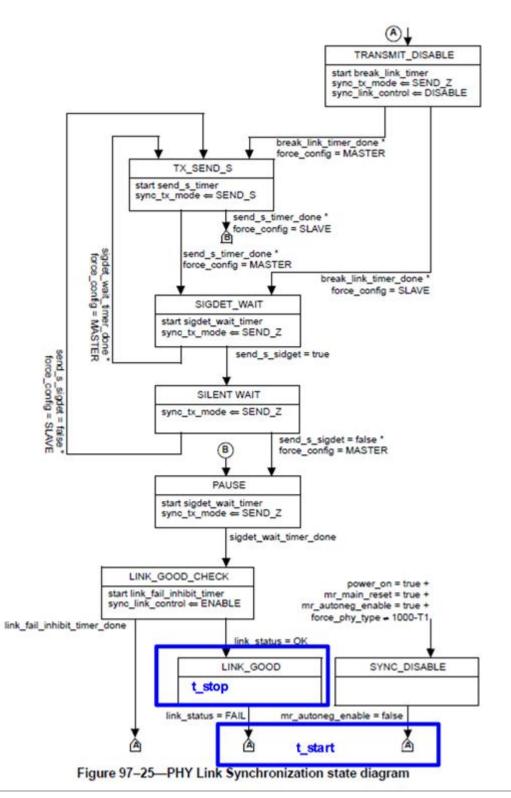

© 2024 OPEN Alliance Dec-24 14 t\_start Start of Linkup\_Total\_Time Counter -- AutoNegotiation State Machine

#### 98.5.5 State diagrams

Figure 4 Linkup\_Total\_Time Start and stop condition for timing measurement at 1000BASE-T1 with Auto-Negotiation

|             | LQ.LTT                                                                                                |

|-------------|-------------------------------------------------------------------------------------------------------|

| Name        | Linkup_Total_Time                                                                                     |

| Description | )<br>Information about the total link up time from enabling the PHY until the link is<br>established. |

| Explanation | 1 Bit == 1ms; max range 2047ms                                                                        |

Table 9 Definition of LQ.LTT

## 6.3.2 Local receiver time (LRT)

#### **Optional or mandatory feature: optional**

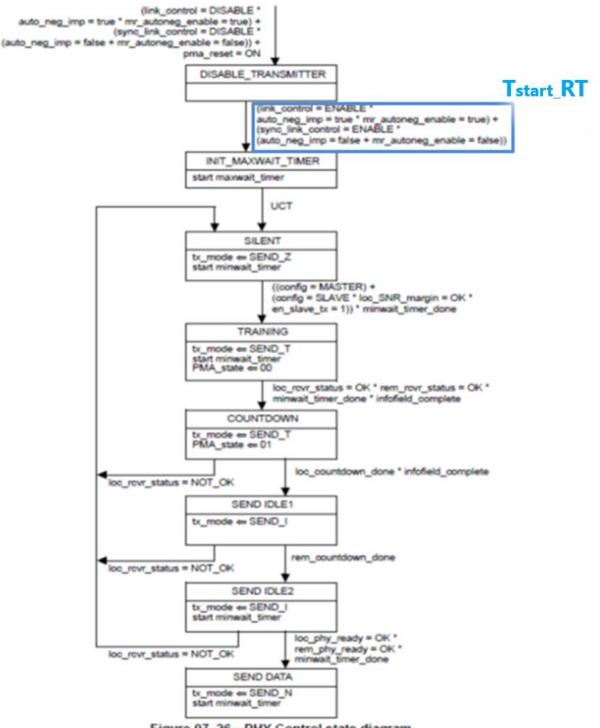

For the last successful training, the transceiver shall provide the time required from PHYC control INIT\_MAXWAIT\_TIMER state until the loc\_phy\_ready = OK. In this context, the following time definitions apply (Tstart\_RT is defined by Figure 5):

#### • 1000BASE-T1

Local Receiver Time (LRT) Tstop\_RT =>loc\_phy\_ready=OK LQ.LRT= Tstop\_RT - Tstart\_RT

|             | LQ.LRT                        |

|-------------|-------------------------------|

| Name        | Local Receiver Time           |

| Description | Time until loc_phy_ready = OK |

| register value | Explanation                   |

|----------------|-------------------------------|

| Explanation    | 1 Bit == 1ms; max range 250ms |

Table 10 Definition of LQ.LRT register

Figure 97–26—PHY Control state diagram

Figure 5 LQ.LRT and LQ.LTT Start condition for timing measurement at 1000BASE-T1

© 2024 OPEN Alliance Dec-24 17

## 6.3.3 Remote receiver time (RRT)

## **Optional or mandatory feature: optional**

For the last successful training, the transceiver shall provide the time required from PHYC control INIT\_MAXWAIT\_TIMER state until the local PHY is signalling that rem\_phy\_ready = OK. In this context, the following time definitions apply (Tstart\_RT as in <u>Subclause 6.3.2</u>):

#### • 1000BASE-T1

Remote Receiver Time (RRT) Tstop\_RT=> rem\_phy\_ready=OK LQ.RRT= Tstop\_RT- Tstart\_RT

|             | LQ.RRT                        |

|-------------|-------------------------------|

| Name        | Remote Receiver Time          |

| Description | Time until rem_phy_ready = OK |

| register value                         | Explanation                   |

|----------------------------------------|-------------------------------|

| Explanation                            | 1 Bit == 1ms; max range 250ms |

| Table 11 Definition of LO DDT register |                               |

Table 11 Definition of LQ.RRT register

## 6.3.4 Link Losses (LL)

#### **Optional or mandatory feature: mandatory**

The PHY shall store the number of link failures which occurred since the last power cycle in a register.

|             | LQ.LFL                                                            |

|-------------|-------------------------------------------------------------------|

| Name        | Link Losses                                                       |

| Description | number of Link Losses which occurred since last power cycle (063) |

| Explanation | 063 link losses occurred                                          |

Table 12 Definition of LQ.LFL register

## 6.3.5 Communication ready status (COM)

#### **Optional or mandatory feature: mandatory**

The Communication\_ready (Comm\_ready) status is an optimized Link\_Status information which shall be provided via the extended status register as information for higher layers to signal that from now on communication via the link is possible.

The optimized link status shall be defined by the Comm ready status, when this meets the system will be confirmed as capable of communicating.

• 1000BASE-T1

Comm\_ready = link status

|             | LQ.COM                             |

|-------------|------------------------------------|

| Name        | Communication Ready Status         |

| Description | information on communication ready |

|             | Explanation                                                            |

|-------------|------------------------------------------------------------------------|

| Explanation | False If !(loc_phy_ready = OK * rem_phy_ready = OK * link_status = OK) |

|             | True If (loc_phy_ready = OK * rem_phy_ready = OK * link_status = OK)   |

Table 13 Definition of LQ.COM

# 6.4 Polarity Detection and Correction (POL)

In accordance with the specifications (1000BASE-T1). No specific diagnostic feature.

# 6.5 Forward Error Correction Counter

## 6.5.1 FEC Counter (FECC)

## **Optional or mandatory feature: mandatory**

The transceiver shall store the number of frames with correctable FEC errors, which occurred since the last power cycle or reset.

|             | FEC.FECC                                                                              |

|-------------|---------------------------------------------------------------------------------------|

| Name        | Forward Error Correction Counter                                                      |

| Description | Number of Frames captured (01023) with symbols corrected by FEC.                      |

|             | Note – Up to 22 symbols could be corrected by FEC without an error / data loss in the |

|             | received data.                                                                        |

| Explanation | 01023 frames corrected                                                                |

| Explanation |                                                                                       |

Table 14 Definition of FEC.FECC

=== End of Document===