# 10BASE-T1S PLCA Conformance Test Suite Specification

PLCA Conformance Test Suite Specification

| Version           | 1.3           |

|-------------------|---------------|

| Date              | June 16, 2025 |

| Status            | Final         |

| Restriction Level | Public        |

|                   |               |

#### **VERSION AND RESTRICTION HISTORY OF THIS DOCUMENT**

| VERSION | DESCRIPTION                                                                                                                                                                                                             | RESTRICTION LEVEL                                                                  | DATE             |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------|

| 0.1     | Initial version                                                                                                                                                                                                         |                                                                                    |                  |

| 0.2     | Implemented Feedback from April 4, 2023                                                                                                                                                                                 |                                                                                    | April 20, 2023   |

| 0.3     | Implemented Feedback from CanovaTech discussed on May 11, 2023                                                                                                                                                          |                                                                                    | May 11, 2023     |

| 0.4     | Following the consensus achieved in the ballot held at the TC14 main regular call on June 20, 2023, the PLCA Recovery section has been defined as informative and the respective pass criteria were updated accordingly | OPEN Members<br>Only                                                               | June 22, 2023    |

| 0.5     | Last editorial feedback from Canovatech<br>and Onsemi of typos and copy/paste errors<br>were corrected                                                                                                                  | ast editorial feedback from Canovatech<br>nd Onsemi of typos and copy/paste errors |                  |

| 1.0     | Public                                                                                                                                                                                                                  |                                                                                    | November 8, 2023 |

| 1.1     | Update considering early testing experience                                                                                                                                                                             |                                                                                    | February 5, 2025 |

| 1.2     | Update includes minor corrections to the equations in Groups T2 & T3 as per the latest feedback from Microchip.                                                                                                         | OPEN Members<br>Only                                                               | March 10, 2025   |

| 1.2a    | Update includes editorial changes as per the latest feedback from OnSemi.                                                                                                                                               |                                                                                    | March 11, 2025   |

| 1.3     | Transferred into new OPEN Template and creation of final version                                                                                                                                                        | Public                                                                             | June 16, 2025    |

# **CHAIR AND VICE CHAIR**

| CHAIR                        | NAME               | ORGANIZATION |

|------------------------------|--------------------|--------------|

| OPEN Alliance TC14 Chair     | Samuel Sigfridsson | Volvo Cars   |

| OPEN Alliance T14 Vice Chair | Patrick Isensee    | C&S Group    |

# **EDITOR**

| NAME           | ORGANIZATION |

|----------------|--------------|

| David Bollati  | C S Croup    |

| Jan Kretschmer | C&S Group    |

# **CONTRIBUTORS**

| NAME               | ORGANIZATION |

|--------------------|--------------|

| Tim Baggett        | Microchip    |

| Piergirogio Beruto | OnSemi       |

| Viliam Vozar       | OnSemi       |

# **Table of Contents**

| V | ERSIC        | ON AND RESTRICTION HISTORY OF THIS DOCUMENT                       | 2    |

|---|--------------|-------------------------------------------------------------------|------|

| С | HAIR         | AND VICE CHAIR                                                    | 2    |

| Ε | DITO         | R                                                                 | 2    |

| С | ONTE         | RIBUTORS                                                          | 2    |

| С | PEN :        | SPECIFICATION OWNERSHIP AND USAGE RIGHTS                          | 5    |

| R | IGHT         | S AND USAGE RESTRICTIONS SPECIFIC TO OPEN ALLIANCE MEMBERS        | 5    |

|   | Rights       | s and Usage Restrictions Specific to Non-members of OPEN Alliance | 5    |

| Т | ERMS         | APPLICABLE TO BOTH MEMBERS AND NON-MEMBERS OF OPEN ALLIANCE       | 6    |

|   | Paten        | nts, Trademarks, and other Rights:                                | 6    |

|   | Discla       | aimers and Limitations of Liability:                              | 6    |

|   | Comp         | oliance with Laws and Regulations:                                | 6    |

|   | Autor        | notive Applications Only:                                         | 7    |

|   | Right        | to Withdraw or Modify:                                            | 7    |

| 1 | INT          | RODUCTION                                                         | 8    |

| 2 | NO           | RMATIVE REFERENCES                                                | 9    |

| 3 | TEF          | RMS AND DEFINITIONS                                               | . 10 |

|   | 3.1          | Node term definition                                              | 10   |

|   | 3.2          | PLCA location within different 10BASE-T1S PHYs implementations    | 11   |

| 4 | AB           | BREVIATION/SYMBOLS                                                | . 12 |

| 5 | GL           | OSSARY TERMS                                                      | . 13 |

| 6 | OR           | GANIZATION OF TESTS                                               | . 14 |

|   | 6.1          | Elementary test structure                                         | 14   |

|   | 6.2          | Test case instance structure                                      | 14   |

|   | 6.3          | DUT requirements                                                  | 15   |

| 7 | PLO          | CA CONFORMANCE TEST DEFINITIONS                                   | . 16 |

|   | 7.1          | Channels definition                                               |      |

|   | 7.1.<br>7.1. | 3                                                                 |      |

|   | 7.2          | PLCA configuration                                                |      |

|   |              |                                                                   |      |

| June 16, 2025 |

|   | 7.2.1    | PLCA configuration in 2 nodes in the mixing segment [H1]   |    |

|---|----------|------------------------------------------------------------|----|

|   | 7.2.2    | PLCA configuration in 3 nodes in the mixing segment [H2]   | 17 |

|   | 7.3 Me   | ssage transfer                                             | 17 |

|   | 7.4 Pov  | ver conditions                                             | 18 |

|   | 7.4.1    | Nominal Battery Voltage                                    | 18 |

| 8 | GROUI    | P 1 – PLCA TEST CASES                                      | 19 |

|   | 8.1 [T]  | PLCA Timing requirements                                   | 19 |

|   | 8.1.1    | Group T1 – Coordinator node                                | 19 |

|   | 8.1.2    | Group T2 – Follower node BEACON                            |    |

|   | 8.1.3    | Group T3 – Follower node packet                            | 24 |

|   | 8.2 [D]  | PLCA Decoding of BEACON and message reception              | 27 |

|   | 8.2.1    | Group D1 – Decoding of BEACON                              | 27 |

|   | 8.3 [R]  | PLCA Recovery                                              | 29 |

|   | 8.3.1    | Group R1 – Recovery of a Coordinator node                  |    |

|   | 8.3.2    | Group R2 – Recovery of a Follower node                     | 31 |

|   | 8.4 [B]  | PLCA Burst                                                 | 33 |

|   | 8.4.1    | 10Group B1 – PLCA burst count > TX buffer                  | 33 |

|   | 8.4.2    | Group B2 – PLCA burst count < TX buffer                    | 35 |

|   | 8.5 [C]  | PLCA Corner cases                                          | 37 |

|   | 8.5.1    | Group C1 – Decoding of COMMIT near to_timer_done           |    |

|   | 8.5.2    | Group C2 – Recovery of coordinator node near to_timer_done | 39 |

|   | 8.5.3    | Group C3 – Recovery of follower node near to_timer_done    | 41 |

| 9 | APPEN    | IDIX                                                       | 43 |

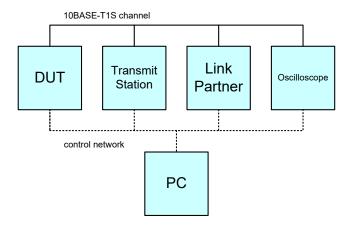

|   | 9.1 Tes  | t station setup                                            | 43 |

|   | 9.1.1    | Transmit Station                                           |    |

|   | 9.1.2    | DUT                                                        | 43 |

|   | 9.1.3    | Link partner                                               | 44 |

|   | 9.2 List | t of Tables                                                | 45 |

|   | 9.3 List | t of Figures                                               | 45 |

|   |          |                                                            |    |

OPEN Alliance Specification Copyright Notice and Disclaimer

#### **OPEN SPECIFICATION OWNERSHIP AND USAGE RIGHTS**

As between OPEN Alliance and OPEN Alliance Members whose contributions were incorporated in this OPEN Specification (the "Contributing Members"), the Contributing Members own the worldwide copyrights in and to their given contributions. Other than the Contributing Members' contributions, OPEN Alliance owns the worldwide copyrights in and to compilation of those contributions forming this OPEN Specification. For OPEN Alliance Members (as that term is defined in the OPEN Alliance Bylaws), OPEN Alliance permits the use of this OPEN Specification on the terms in the OPEN Alliance Intellectual Property Rights Policy and the additional applicable terms below. For non-members of OPEN Alliance, OPEN Alliance permits the use of this OPEN Specification on the terms in the OPEN Alliance Specification License Agreement (available here: http://www.opensig.org/Automotive-Ethernet-Specifications/) and the additional applicable terms below. The usage permissions referenced and described here relate only to this OPEN Specification and do not include or cover a right to use any specification published elsewhere and referred to in this OPEN Specification. By using this OPEN Specification, you hereby agree to the following terms and usage restrictions:

#### RIGHTS AND USAGE RESTRICTIONS SPECIFIC TO OPEN ALLIANCE MEMBERS

FOR OPEN ALLIANCE MEMBERS ONLY: In addition to the usage terms and restrictions granted to Members in the OPEN Alliance Intellectual Property Rights Policy, Members' use of this OPEN Specification is subject this Copyright Notice and Disclaimer. Members of OPEN Alliance have the right to use this OPEN Specification solely (i) during the term of a Member's membership in OPEN Alliance and subject to the Member's continued membership in good standing in OPEN Alliance; (ii) subject to the Member's continued compliance with the OPEN Alliance governance documents, Intellectual Property Rights Policy, and the applicable OPEN Alliance Promoter or Adopter Agreement, as applicable; and (iii) for internal business purposes and solely to use the OPEN Specification for implementation of this OPEN Specification in the Member's products and services, but only so long as Member does not distribute, publish, display, or transfer this OPEN Specification to any third party, except as expressly set forth in Section 11 of the OPEN Alliance Intellectual Property Rights Policy. Except and only to the extent required to use this OPEN Specification internally for implementation of this OPEN Specification in Member's products and services, Member shall not modify, alter, combine, delete portions of, prepare derivative works of, or create derivative works based upon this OPEN Specification. If Member creates any modifications, alterations, or other derivative works of this OPEN Specification as permitted to use the same internally for implementation of this OPEN Specification in Member's products and services, all such modifications, alterations, or other derivative works shall be deemed part of, and licensed to such Member under the same restrictions as, this OPEN Specification. For the avoidance of doubt, Member shall not include all or any portion of this OPEN Specification in any other technical specification or technical material, product manual, marketing material, or any other material without OPEN Alliance's prior written consent. All rights not expressly granted to Member in the OPEN Alliance Intellectual Property Rights Policy are reserved.

# Rights and Usage Restrictions Specific to Non-members of OPEN Alliance

FOR NON-MEMBERS OF OPEN ALLIANCE ONLY: Use of this OPEN Specification by anyone who is not a Member in good standing of OPEN Alliance is subject to your agreement to the OPEN Alliance Specification License Agreement (available here: <a href="http://www.opensig.org/Automotive-Ethernet-Specifications/">http://www.opensig.org/Automotive-Ethernet-Specifications/</a>) and the additional terms in this Copyright Notice and Disclaimer. Non-members have the right to use this OPEN Specification solely (i) subject to the non-member's continued compliance with the OPEN Alliance Specification License Agreement; and (ii) for internal business purposes and solely to use the OPEN Specification for implementation of this OPEN Specification in the non-member's products and services, but only so long as non-member does not distribute, publish, display, or transfer this OPEN Specification to any third party, unless and only to the extent expressly set forth in the OPEN Alliance Specification License

Agreement. Except and only to the extent required to use this OPEN Specification internally for implementation of this OPEN Specification in non-member's products and services, non-member shall not modify, alter, combine, delete portions of, prepare derivative works of, or create derivative works based upon this OPEN Specification. If non-member creates any modifications, alterations, or other derivative works of this OPEN Specification as permitted to use the same internally for implementation of this OPEN Specification in non-member's products and services, all such modifications, alterations, or other derivative works shall be deemed part of, and licensed to such non-member under the same restrictions as, this OPEN Specification. For the avoidance of doubt, non-member shall not include all or any portion of this OPEN Specification in any other technical specification or technical material, product manual, marketing material, or any other material without OPEN Alliance's prior written consent. All rights not expressly granted to non-member in the OPEN Alliance Specification License Agreement are reserved.

#### TERMS APPLICABLE TO BOTH MEMBERS AND NON-MEMBERS OF OPEN ALLIANCE

#### Patents, Trademarks, and other Rights:

OPEN Alliance has received no Patent Disclosure and Licensing Statements related to this OPEN Specification. Therefore, this OPEN Specification contains no specific disclaimer related to third parties that may require a patent license for their Essential Claims. Having said that, the receipt of this OPEN Specification shall not operate as an assignment of or license under any patent, industrial design, trademark, or other rights as may subsist in or be contained in or reproduced in this OPEN Specification; and the implementation of this OPEN Specification could require such a patent license from a third party. You may not use any OPEN Alliance trademarks or logos without OPEN Alliance's prior written consent.

#### **Disclaimers and Limitations of Liability:**

THIS OPEN SPECIFICATION IS PROVIDED ON AN "AS IS" BASIS, AND ALL REPRESENTATIONS, WARRANTIES, AND GUARANTEES, EITHER EXPLICIT, IMPLIED, STATUTORY, OR OTHERWISE, ARE EXCLUDED AND DISCLAIMED UNLESS (AND THEN ONLY TO THE EXTENT THEY ARE) MANDATORY UNDER LAW. ACCORDINGLY, OPEN ALLIANCE AND THE CONTRIBUTING MEMBERS MAKE NO REPRESENTATIONS OR WARRANTIES OR GUARANTEES WITH REGARD TO THIS OPEN SPECIFICATION OR THE INFORMATION (INCLUDING ANY SOFTWARE) CONTAINED HEREIN. OPEN ALLIANCE AND ALL CONTRIBUTING MEMBERS HEREBY EXPRESSLY DISCLAIM ANY AND ALL SUCH EXPRESS, IMPLIED, STATUTORY, AND ALL OTHER REPRESENTATIONS, WARRANTIES, AND GUARANTEES, INCLUDING WITHOUT LIMITATION ANY AND ALL WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR USE, TITLE, NON-INFRINGEMENT OF OR ABSENCE OF THIRD PARTY RIGHTS, AND/OR VALIDITY OF RIGHTS IN THIS OPEN SPECIFICATION; AND OPEN ALLIANCE AND THE CONTRIBUTING MEMBERS MAKE NO REPRESENTATIONS AS TO THE ACCURACY OR COMPLETENESS OF THIS OPEN SPECIFICATION OR ANY INFORMATION CONTAINED HEREIN, WITHOUT LIMITING THE FOREGOING, OPEN ALLIANCE AND/OR CONTRIBUTING MEMBERS HAS(VE) NO OBLIGATION WHATSOEVER TO INDEMNIFY OR DEFEND YOU AGAINST CLAIMS RELATED TO INFRINGEMENT OR MISAPPROPRIATION OF INTELLECTUAL PROPERTY RIGHTS. OPEN ALLIANCE AND CONTRIBUTING MEMBERS ARE NOT, AND SHALL NOT BE, LIABLE FOR ANY LOSSES, COSTS, EXPENSES, OR DAMAGES OF ANY KIND WHATSOEVER (INCLUDING WITHOUT LIMITATION DIRECT, INDIRECT, SPECIAL, INCIDENTAL, CONSEQUENTIAL, PUNITIVE, AND/OR EXEMPLARY DAMAGES) ARISING IN ANY WAY OUT OF USE OR RELIANCE UPON THIS OPEN SPECIFICATION OR ANY INFORMATION HEREIN. NOTHING IN THIS DOCUMENT OPERATES TO LIMIT OR EXCLUDE ANY LIABILITY FOR FRAUD OR ANY OTHER LIABILITY WHICH IS NOT PERMITTED TO BE EXCLUDED OR LIMITED BY OPERATION OF LAW.

#### **Compliance with Laws and Regulations:**

NOTHING IN THIS DOCUMENT OBLIGATES OPEN ALLIANCE OR CONTRIBUTING MEMBERS TO PROVIDE YOU WITH SUPPORT FOR, OR RELATED TO, THIS OPEN SPECIFICATION OR ANY IMPLEMENTED PRODUCTS OR SERVICES. NOTHING IN THIS OPEN SPECIFICATION CREATES ANY WARRANTIES OR GUARANTEES, EITHER EXPRESS OR IMPLIED, STATUTORY OR OTHERWISE, REGARDING ANY LAW OR REGULATION. OPEN ALLIANCE AND CONTRIBUTING MEMBERS EXPRESSLY DISCLAIM ALL LIABILITY, INCLUDING WITHOUT LIMITATION, LIABILITY FOR NONCOMPLIANCE WITH LAWS, RELATING TO USE OF THE OPEN SPECIFICATION OR INFORMATION CONTAINED HEREIN. YOU ARE SOLELY RESPONSIBLE FOR THE COMPLIANCE OF IMPLEMENTED PRODUCTS AND SERVICES WITH ANY SUCH LAWS AND REGULATIONS, AND FOR OBTAINING ANY AND ALL REQUIRED AUTHORIZATIONS, PERMITS, AND/OR LICENSES FOR IMPLEMENTED PRODUCTS AND SERVICES RELATED TO SUCH LAWS AND REGULATIONS WITHIN THE APPLICABLE JURISDICTIONS.

IF YOU INTEND TO USE THIS OPEN SPECIFICATION, YOU SHOULD CONSULT ALL APPLICABLE LAWS AND REGULATIONS. COMPLIANCE WITH THE PROVISIONS OF THIS OPEN SPECIFICATION DOES NOT CONSTITUTE COMPLIANCE TO ANY APPLICABLE LEGAL OR REGULATORY REQUIREMENTS. IMPLEMENTERS OF THIS OPEN SPECIFICATION ARE SOLELY RESPONSIBLE FOR OBSERVING AND COMPLYING WITH THE APPLICABLE LEGAL AND REGULATORY REQUIREMENTS. WITHOUT LIMITING THE FOREGOING, YOU SHALL NOT USE, RELEASE, TRANSFER, IMPORT, EXPORT, AND/OR RE-EXPORT THIS OPEN SPECIFICATION OR ANY INFORMATION CONTAINED HEREIN IN ANY MANNER PROHIBITED UNDER ANY APPLICABLE LAWS AND/OR REGULATIONS, INCLUDING WITHOUT LIMITATION U.S. EXPORT CONTROL LAWS.

#### **Automotive Applications Only:**

Without limiting the foregoing disclaimers or limitations of liability in any way, this OPEN Specification was developed for automotive applications only. This OPEN Specification has neither been developed, nor tested for, non-automotive applications.

# Right to Withdraw or Modify:

OPEN Alliance reserves the right to (but is not obligated to) withdraw, modify, or replace this OPEN Specification at any time, without notice.

© 2025 OPEN Alliance. This document also contains contents, the copyrights of which are owned by third parties who are OPEN Alliance Contributing Members. Unauthorized Use Strictly Prohibited. All Rights Reserved.

#### 1 INTRODUCTION

This suite of tests has been developed to help implementers evaluate the functionality of the PLCA reconciliation sublayer of their 10BASE-T1S device.

These tests are designed to determine if a product conforms to specifications defined in IEEE802.3cg Clause 148. Successful completion of all tests contained in this suite does not guarantee that the tested device will operate with other devices. However, combined with satisfactory operation when tested in accordance with the OPEN Alliance 10BASE-T1S Interoperability Test Suite, these tests provide a reasonable level of confidence that the Device Under Test (DUT) will function properly in many 10BASE-T1S automotive environments.

#### 2 NORMATIVE REFERENCES

The following documents are referred to in the text in such a way that some or all their content constitutes requirements of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

- [1] IEEE P802.3cg: Physical Layer Specifications and Management Parameters for 10 Mb/s Operation and Associated Power Delivery over a Single Balanced Pair of Conductors

- [2] OPEN ALLIANCE: 10BASE-T1S Physical Media Attachment Test Suite Revision 1.2 (draft)

- [3] OPEN ALLIANCE: 10BASE-T1S Physical Coding Sublayer Test Suite Revision 0.3 (draft)

- [4] OPEN ALLIANCE: Channel and Components Requirements for 10BASE-T1S Link Segment Revision 0.2 (draft)

- [5] OPEN ALLIANCE: IEEE 10BASE-T1S System Implementation Specification Revision 1.0

- [6] OPEN ALLIANCE: 10BASE-T1S PLCA Management Registers Revision 1.2

- [7] ISO/IEC 9646 Information technology Open Systems Interconnection Conformance testing methodology and framework

- [8] OPEN ALLIANCE: 10BASE-T1x MAC-PHY Serial Interface Revision 1.1

#### 3 TERMS AND DEFINITIONS

For the purposes of this document, the following terms and definitions apply.

ISO and IEC maintain terminological databases for use in standardization at the following addresses:

- ISO Online browsing platform: available at <a href="https://www.iso.org/obp">https://www.iso.org/obp</a>

- IEC Electropedia: available at <a href="http://www.electropedia.org/">http://www.electropedia.org/</a>

#### 3.1 Node term definition

| End Node    | A node that is at either end of a mixing segment. There are no other nodes between the End Node and the $100\Omega$ edge termination. The End Node may contain the $100\Omega$ edge termination. |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Drop Node   | Any node that is located between the two end nodes                                                                                                                                               |  |

| Coordinator | This is the node configured as aPLCALocalNodeID=0 that is responsible for the periodic transmission of the BEACON and configuring the number of transmit opportunities between each BEACON.      |  |

| Follower    | Followers are any nodes configured as aPLCALocalNodeID=1254. They synchronize their transmit opportunity counter with the reception of the periodic BEACON transmitted by the coordinator        |  |

| Head Node   | This is the highest-level application node on the mixing segment. It typically implements a switch or gateway access to the core network beyond the bus segment.                                 |  |

Note: It is expected that each network segment includes one Coordinator Node, one Head Node, and two End Nodes. The Coordinator and Head Node functions may be implemented in any physical node (including End Nodes) and may be combined into a single physical node or separate physical nodes.

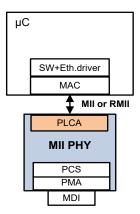

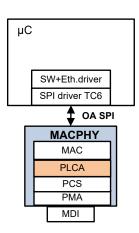

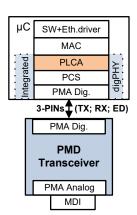

#### 3.2 PLCA location within different 10BASE-T1S PHYs implementations

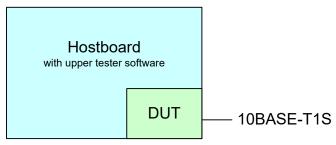

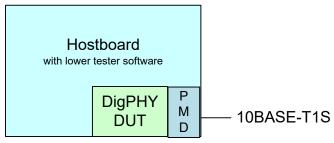

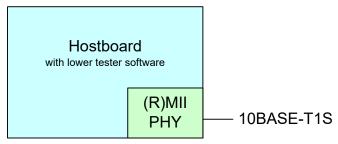

Following table describes an overview of the different possible 10BASE-T1S PHYs implementations that are covered by this test specification.

#### **PHY with MII**

PLCA integrated in PHY: transparent for every uC

Compatible with every MAC controller supporting Half-duplex

# **PHY with SPI (MACPHY)**

Low-cost ECU without MAC and smaller interface

Requires Ethernet frame processing over SPI interface as defined in [8].

## **DigPHY/PMD Transceiver**

The 10BASE-T1S PMD Transceiver is a simple and cost effective solution with 3-pin clock-less interface between the host controller and the PMD transceiver chip suited for embedded systems where the digital portion of the PHY is fully integrated into an MCU, an Ethernet switch core, or any other suitable host where only the analog portion is left into a separate chip (i.e., the PMD transceiver).

# 4 ABBREVIATION/SYMBOLS

| Abbreviation | Glossary term                                                                                                        | Glossary definition                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dPLCA        | Dynamic Physical<br>Layer Collision<br>Avoidance                                                                     | It is an optional PLCA Node ID allocation method. This should allow all node IDs (including node 0) to be assigned dynamically and to change during operation. The coordinator node shall also be able to vary the node count depending on how many active nodes are detected. dPLCA is fully backward compatible to the normal PLCA defined in 802.3cg, so that dPLCA enabled nodes can join a network with normal PLCA nodes without disturbing the operation. |

| DUT          | Device under test                                                                                                    | Combination of uC, PHY/Switch component, PHY/Switch configuration and filter that is being tested.                                                                                                                                                                                                                                                                                                                                                               |

| IUT          | Implementation under test                                                                                            | The PHYs entirely in a network environment are considered as the IUT                                                                                                                                                                                                                                                                                                                                                                                             |

| MAC          | Media Access<br>Control                                                                                              | Abbreviation for the sub layer of the data link layer (layer 2) of the OSI model or for the physical device that implements the Media Access Control functions.                                                                                                                                                                                                                                                                                                  |

| MDI          | Media dependent interface                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MII          | Medium<br>Independent<br>Interface                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P2P          | Point-to-point                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PCS          | Physical Coding<br>Sublayer                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PHY          | Interface<br>semiconductor<br>circuit for<br>implementation of<br>the functions of the<br>Ethernet physical<br>layer | Abbreviation for the physical layer (layer 1) of the OSI model or for the device that implements layer 1 of the OSI model.                                                                                                                                                                                                                                                                                                                                       |

| PLCA         | Physical Layer<br>Collision Avoidance                                                                                | A method for generating transmit opportunities for 10BASE-T1S operating on mixing segments. (See[1], Clause 148.)                                                                                                                                                                                                                                                                                                                                                |

| РМА          | Physical Medium<br>Attachment                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SPI          | Serial Peripheral<br>Interface                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ТО           | Transmit opportunity                                                                                                 | Each node on the network get assigned at least one transmit opportunity in each transmission cycle.                                                                                                                                                                                                                                                                                                                                                              |

| n.a.         | Not applicable                                                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Table 1: List of Abbreviations.

# **5 GLOSSARY TERMS**

| Glossary term                           | Glossary definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAY                                     | This word or the adjective "OPTIONAL", means that an item is truly optional. One vendor may choose to include the item because a particular marketplace requires it or because the vendor feels that it enhances the product while another vendor may omit the same item. An implementation which does not include a particular option MUST be prepared to interoperate with another implementation which does include the option, though perhaps with reduced functionality. In the same way an implementation which does include a particular option MUST be prepared to interoperate with another implementation which does not include the option (except, of course, for the feature the option provides.) |

| MUST                                    | This word, or the terms "REQUIRED" or "SHALL", means that the definition is an absolute requirement of the specification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MUST NOT                                | This phrase or the phrase "SHALL NOT", means that the definition is an absolute prohibition of the specification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SHOULD                                  | This word, or the adjective "RECOMMENDED", means that there may exist valid reasons in particular circumstances to ignore a particular item, but the full implications must be understood and carefully weighed before choosing a different course.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SHOULD NOT                              | This phrase, or the phrase "NOT RECOMMENDED" means that there may exist valid reasons in particular circumstances when the particular behavior is acceptable or even useful, but the full implications should be understood, and the case carefully weighed before implementing any behavior described with this label.                                                                                                                                                                                                                                                                                                                                                                                         |

| External PHY filter or external filter. | An additional circuit that is connected directly to the PHY and filters the in- and outgoing physical layer signaling. The PHY vendor typically provides a reference filter design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PHY configuration                       | Variable settings that affect the PHY's behavior (e.g., sensitivity of internal equalizers, or shaping of outgoing physical layer signaling). The PHY configuration could be set by an upper layer (e.g., by software) or could be hardcoded, e.g., via dedicated PHY configuration pins.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Test case                               | Description of one or more test steps and a set of conditions that define whether the observed behavior when executing the test steps matches the expected results.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Test iteration                          | The execution of all test steps of a given test case.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Test instance                           | A test instance defines different test parameters for a given test case, such as the DUT's PHY Coordinator/Follower configuration, or used cable to connect the link partner. The test case itself is not altered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Channel                                 | Synonym for physical layer communication channel (cf. [4]).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Table 2: List of Definitions.

#### **6 ORGANIZATION OF TESTS**

In this chapter the main structure of the test cases as well as the elementary test case structure will be introduced.

#### 6.1 Elementary test structure

The main structure description of a test case is shown in Table 3. A brief description of the meaning of each field is provided.

| Purpose             | A short description of the purpose of the test case is given here.                                                                                                        |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Reference           |                                                                                                                                                                           |  |

| Prerequisites       | A list of requirements and capabilities needed for proper test conduction                                                                                                 |  |

| DUT set-up          | The respective test environment setup is specified (e. g. if different test case sequences will require different test system configuration)                              |  |

|                     | The first note here describes the total sum of test case executions due to setup variations to give the test implementer a first impression of the specific test case.    |  |

| Test<br>description | As the second part of the test case execution, the test steps are described dealing with the setup being applied and what is observed and measured at each execution etc. |  |

|                     | All actions of the test environment shall be described explicitly in this item.                                                                                           |  |

| Pass criteria       | In this response cell, a description is given about what is expected as the result.  Pass criteria are also specified in this point.                                      |  |

| Test<br>iterations  | Amount of test repetitions.                                                                                                                                               |  |

| Notes               | When necessary, a note will be added complementing the information of the test case.                                                                                      |  |

Table 3 - Main test structure

#### 6.2 Test case instance structure

Together with the test definition and all its parameters, the test case instances that are part of each test case will also be defined. A test case instance can be defined as a repetition of the same test case modifying certain configurations of the DUT and the test environment without losing focus on the test purpose.

| Instance<br>Test Case # | Description                                              | Parameter | Condition                                                        |

|-------------------------|----------------------------------------------------------|-----------|------------------------------------------------------------------|

| AX.XX                   | Description of the test cases belonging to this subgroup | α         | conditions under which the variables are                         |

| AX.XX                   |                                                          | β         | applied either in different configurations or stress conditions. |

Table 4 - Test case instance definition

#### 6.3 **DUT** requirements

For the purposes of this test suite, it is assumed that the DUT can manipulate PLCA-related signals and ID numbers via registers. In addition, at least one or more nodes are required for PLCA testing. This node must be able to set the ID to any number from 0, 255, 1-254.

#### 7 PLCA CONFORMANCE TEST DEFINITIONS

#### 7.1 Channels definition

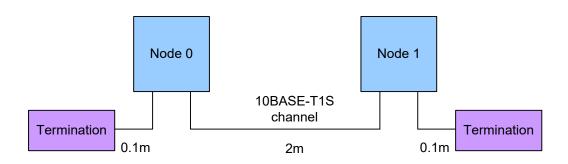

This definition shall be used for defining a test wiring harness that simulates various communication channels according to the channel definitions of IEEE Std. 802.3cg, [4] and [5].

# 7.1.1 Channel type 1 (2 node mixing segment) [H1]

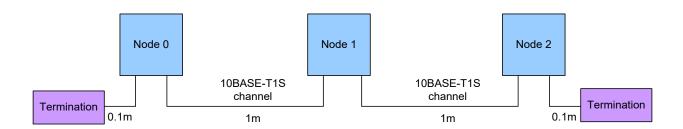

#### 7.1.2 Channel type 2 (3 node mixing segment) [H2]

#### 7.2 PLCA configuration

PLCA parameters not mentioned here shall be set to "default" according to [6] and [1]. dPLCA is outside the scope of this document.

# 7.2.1 PLCA configuration in 2 nodes in the mixing segment [H1]

The nodes are numbered from 0 to 1. Node 0 is configured to be the coordinator. The maximum slot number (TO) is 1, so that the beacon follows immediately after the message send from node 1.

The amount of data per message and the data itself that is to be sent in each message is defined in the section 7.3.

| PLCA slot | 0 | 1 | 0 |

|-----------|---|---|---|

| Node      | 0 | 1 | 0 |

| Burst     | 1 | 1 |   |

Figure 7-1: PLCA cycle in 2 nodes mixing segment [H1]

#### 7.2.2 PLCA configuration in 3 nodes in the mixing segment [H2]

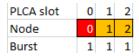

The nodes are numbered from 0 to 2. Node 0 is configured to be the coordinator. The maximum slot number (TO) is 2, so that the beacon follows immediately after the message sent from node 2.

The amount of data per message and the data itself that is to be sent in each message is defined in the section 7.3.

Figure 7-2: PLCA cycle in 3 nodes mixing segment [H2]

#### 7.3 Message transfer

When messages are sent, PLCA is active on all nodes.

M1: all frames have maximum length (1500 bytes in the data field)

- M1A: all nodes in the mixing segment transmit messages

- M1B: only the DUT as Coordinator transmits messages

- M1C: only the DUT as Follower transmit messages

M2: No data is sent, so all TO slots are empty, i.e. without transmission.

M3: Only the Coordinator node sends BEACON and data in TO#0

The addresses in a frame shall be:

- Destination address DA = Broadcast, so all nodes can check counters and report an error (within their frames)

- Source address

SA = Unique in each node

Each node shall maintain and transmit the following parameters:

CycleCounter (CC) (16 bit) increases when the message sent by the Coordinator has been received; this message can be identified by the source address (SA).

SequenceNumber (SC) (8 bit), recent number of messages in a burst. The sequence number indicates the last received frame of a burst. The node sending the burst increments the sequence number by 1 after each successfully sent frame until the maximum number of burst frames for the node is reached.

MessageCounter (MC) (32 bit), increases, with each message sent by this node

#### StatusInformation (SI) (16 bit), to be defined:

- state of health (PLCA Status, SQI if supported, local/remote jabber indication),

- information to synchronize stress conditions applied alternating and cyclically in a decentralized manner like for example loss of power or variable terminations.

- dedicated Request commands (for example, node 0 can request other nodes to reset counters or to stop communication and enter low power mode).

#### aPLCALocalNodeID (PLCA ID) (8 bit), static value

(10 bytes data field up to here, remaining 1490 bytes for padding)

Data field layout: [CC, SC, MC, SI, PLCA ID, Padding]

#### Padding pattern in M1 (fixed length 1490 bytes):

| [0xFF, 0xFE  | ,0x01, 0x00]      | 256 bytes, decreasing                  |

|--------------|-------------------|----------------------------------------|

| 64 x [0x00]  |                   | 64 bytes constant 0x00                 |

| [0x00, 0x01  | , 0xFE, 0xFF]     | 256 bytes, increasing                  |

| 64x [0xFF]   |                   | 64 bytes constant 0xFF                 |

| [0x0F, 0x0E  | ,0xF1, 0xF0]      | 256 bytes, decreasing, XORed with 0xF0 |

| 64x [0xAA]   |                   | 64 bytes constant 0xAA                 |

| [0xF0, 0xF1  | , 0x0E, 0x0F]     | 256 bytes, increasing, XORed with 0xF0 |

| 64x [0x5A]   |                   | 64 bytes constant 0x5A                 |

| Followed by  |                   |                                        |

| 210 x [0x3C] | 210 bytes constan | t 0x3C                                 |

#### 7.4 Power conditions

## 7.4.1 Nominal Battery Voltage

Unless differently indicated the nominal battery voltage used in this specification is 14V  $\pm$  0.1V.

# 8 GROUP 1 – PLCA TEST CASES

# 8.1 [T] PLCA Timing requirements

The test cases defined in this section shall ensure that the PLCA is able to communicate within the required timing parameters.

# 8.1.1 Group T1 – Coordinator node

|               | •                                                                                                                                                                                                                               |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Purpose       | The purpose of this test is to verify important timing parameters for interoperability of nodes in PLCA mode.                                                                                                                   |  |  |

| ruipose       | Under any circumstance, a packet sent by a node during its own TO shall be received by any other node within the corresponding TO boundaries.                                                                                   |  |  |

| Reference     | [1], Table 147-6 10BASE-T1S delay constraints                                                                                                                                                                                   |  |  |

|               | DUT with the capability to reset and configure its PHY.                                                                                                                                                                         |  |  |

| Prerequisites | <ol> <li>DUT shall be able to be configured either as Coordinator node or as Follower<br/>node.</li> </ol>                                                                                                                      |  |  |

|               | 3. DUT must be able to indicate PLCA status via its status registers.                                                                                                                                                           |  |  |

|               | 4. DUT must be able to send frames in the respective transmit opportunity.                                                                                                                                                      |  |  |

|               | This test case is conducted with H1 topology (P2P link segment)                                                                                                                                                                 |  |  |

|               | 2. This test case is conducted with nodes in a mixing-segment multi drop.                                                                                                                                                       |  |  |

|               | aPLCANodeCount = 2                                                                                                                                                                                                              |  |  |

|               | aPLCATransmitOpportunityTimer = 32                                                                                                                                                                                              |  |  |

|               | 3. DUT should be configured as Coordinator node with aPLCALocalNodeID = 0.                                                                                                                                                      |  |  |

|               | 4. DUT shall be ready to transmit before BEACON.                                                                                                                                                                                |  |  |

|               | 5. The used MessageTransfer_M1B is defined in section 7.3.                                                                                                                                                                      |  |  |

| DUT set-up    | Node 0 DUT  Node 1 Transmit Station  10BASE-T1S channel                                                                                                                                                                         |  |  |

|               | Termination 0.1m 2m 0.1m                                                                                                                                                                                                        |  |  |

|               | Figure 8-1: Topology for test group T1                                                                                                                                                                                          |  |  |

|               | <ol> <li>Once the configuration in all nodes is completed, enable the PLCA<br/>reconciliation sublayer functionality at Follower Node and subsequently at<br/>the coordinator node (Node #0) to start communication.</li> </ol> |  |  |

| Test          | <ol><li>Test should wait for PLCA on all nodes to be activated before continuing with<br/>next step.</li></ol>                                                                                                                  |  |  |

| description   | <ol> <li>Initiate data transmission following the respective PLCA Cycle and Message<br/>transfer configurations.</li> </ol>                                                                                                     |  |  |

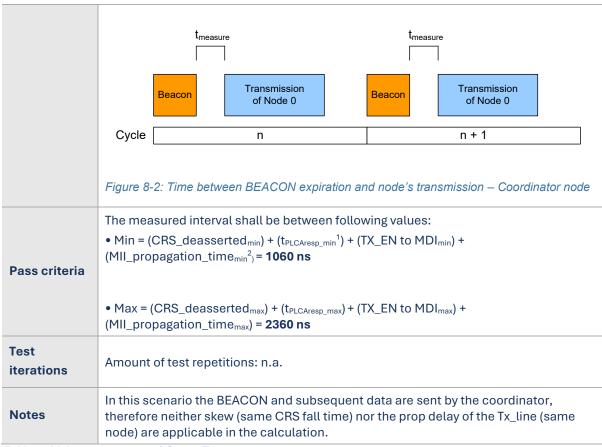

|               | 4. Measure the time between BEACON expiration and node's transmission with an oscilloscope (oscilloscope probe is connected at MDI of the coordinator DUT), as shown as t <sub>measure</sub> in the figure below:               |  |  |

Table 5: Main test structure of Group T1

| Instance<br>Test Case # | Description                      | Parameter | Condition |

|-------------------------|----------------------------------|-----------|-----------|

| T1.1                    | Normal communication undisturbed | n.a.      | n.a.      |

Table 6 - Test case instances definition for Group T1 - Tests case T1.1

RESTRICTION LEVEL: Public | June 16, 2025 | OPEN Alliance, Inc. Page | 20

<sup>&</sup>lt;sup>1</sup> This is the PLCA RS response time. This is the time that it takes for the PLCA state machines to perform an action and transition to new states following the de-assertion of carrier sense. This time is not zero, it is assumed to be minimum = 300 ns and maximum 800ns (the wake/sleep specification added a couple states to the PLCA Control state diagram which requires extra time) and must be accounted for.

<sup>&</sup>lt;sup>2</sup> From the IEEE formalism point of view, there is a propagation time for the MII of 2 clock cycles (max. 800ns), however this is only applicable for external PLCA implementations, implementing PLCA external to the PHY makes no sense, it is assumed 0 ns for an internal PLCA/PHY implementation.

# 8.1.2 Group T2 - Follower node BEACON

| Purpose             | The purpose of this test is to verify important timing parameters for interoperability of nodes in PLCA mode.  Under any circumstance, a packet sent by a node during its own TO shall be received by any other node within the corresponding TO boundaries.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Reference           | [1], Table 147-6 10BASE-T1S delay constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Prerequisites       | <ol> <li>DUT with the capability to reset and configure its PHY.</li> <li>DUT shall be able to be configured either as Coordinator node or as Follower node.</li> <li>DUT must be able to indicate PLCA status via its status registers.</li> <li>DUT must be able to send frames in the respective transmit opportunity.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| DUT set-up          | <ol> <li>This test case is conducted with H1 topology (P2P link segment)</li> <li>This test case is conducted with either nodes mixing-segment multi drop topology or with an arbitrary waveform generator capable to emulate a BEACON pattern (Node#3).         <ul> <li>aPLCANodeCount = 2</li> <li>aPLCATransmitOpportunityTimer = 32</li> </ul> </li> <li>DUT should be configured as Follower node with aPLCALocalNodeID = 1.</li> <li>DUT shall be ready to transmit before BEACON.</li> <li>The used MessageTransfer_M1C is defined in section 7.3.</li> <li>To avoid having the test being affected by the MAC inter-packet gap, allow at least 10us of line idle (no transmissions) before starting the test.</li> <li>Expiration of TO timer needs to be considered.</li> </ol> Node 0 Transmit Station Node 0 Transmit Station Termination         0.1m Termination Termination Termination O.1m Termination Figure 8-3: Topology for test group T2 |  |  |

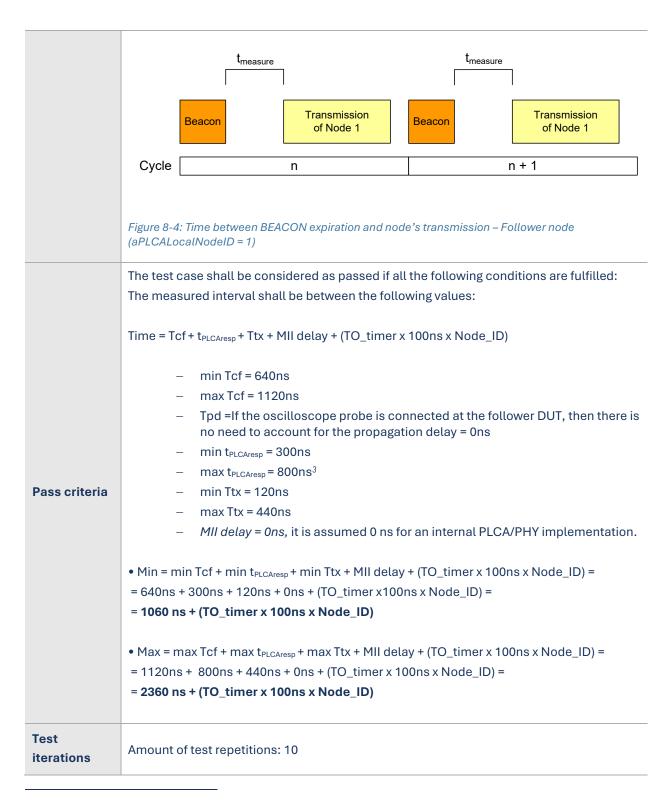

| Test<br>description | <ol> <li>Once the configuration in all nodes is completed, enable the PLCA reconciliation sublayer functionality at Follower Node and subsequently at the coordinator node (Node #0) to start communication.</li> <li>Test should wait for PLCA on all nodes to be activated before continuing with next step.</li> <li>Initiate data transmission with the respective PLCA Cycle and Message transfer.</li> <li>Measure the time between BEACON expiration and node's transmission with an oscilloscope (oscilloscope probe is connected at the MDI of the follower DUT), as shown as t<sub>measure</sub> in the figure below:</li> </ol>                                                                                                                                                                                                                                                                                                                     |  |  |

<sup>&</sup>lt;sup>3</sup> The wake/sleep specification added a couple states to the PLCA Control state diagram which requires extra time.

Notes

Table 7: Main test structure of Group T2

| Instance<br>Test Case # | Description                                                | Parameter                                                                                                                                                                           | Condition                                                                                             |

|-------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| T2.1                    | PLCA Timing<br>requirements –<br>Follower Node -<br>BEACON | Node_ID = from 1 to 16 The aPLCANodeCount should be incremented accordingly when Node_ID >1 TO_TIMER = minimum value declared by the PHY manufacturer <sup>4</sup> , 32, 36 and 40. | repeat the test with different values of TO_TIMER and different values of the node ID/aPLCANodeCount. |

Table 8 - Test case instances definition for Group T2 - Tests case T2.1

RESTRICTION LEVEL: Public | June 16, 2025 | OPEN Alliance, Inc. Page | 23

$<sup>^4</sup>$  **TO\_TIMER** = 28 will be considered if no minimum value is declared by the PHY manufacturer.

# 8.1.3 Group T3 – Follower node packet

| Purpose             | The purpose of this test is to verify important timing parameters for interoperability of nodes in PLCA mode.  Under any circumstance, a packet sent by a node during its own TO shall be received by any other node within the corresponding TO boundaries.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Reference           | [1], Table 147-6 10BASE-T1S delay constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Prerequisite<br>s   | <ol> <li>DUT with the capability to reset and configure its PHY.</li> <li>DUT shall be able to be configured either as Coordinator node or as Follower node.</li> <li>DUT must be able to indicate PLCA status via its status registers.</li> <li>DUT must be able to send frames in the respective transmit opportunity.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| DUT set-up          | <ol> <li>DUT must be able to send frames in the respective transmit opportunity.</li> <li>This test case is conducted with H1 topology (P2P link segment)</li> <li>This test case is conducted with either nodes mixing-segment multi drop topology or with an arbitrary waveform generator capable to emulate a BEACON pattern (Node#1).         <ul> <li>aPLCANodeCount = 2</li> <li>aPLCATransmitOpportunityTimer = 32</li> </ul> </li> <li>DUT shall be ready to transmit before BEACON.</li> <li>The used MessageTransfer_M1A is defined in section 7.3.</li> <li>To avoid having the test being affected by the MAC inter-packet gap, allow at least 10us of line idle (no transmissions) before starting the test.</li> <li>Expiration of TO timer needs to be taken into account.</li> </ol> Node 0 Transmit Station Termination O.1m Termination Termination Termination Termination Termination |  |  |

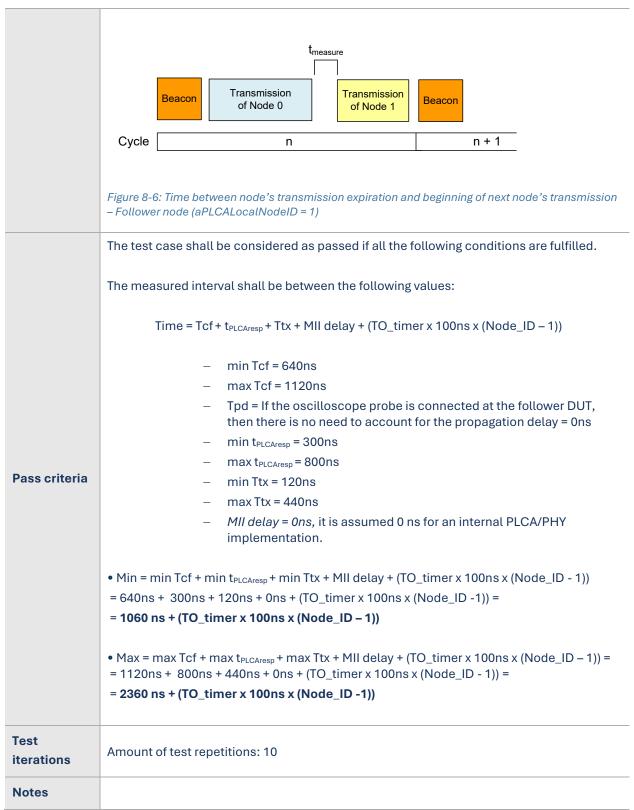

| Test<br>description | <ol> <li>Once the configuration in all nodes is completed, enable the PLCA reconciliation sublayer functionality at Follower Node and subsequently at the coordinator node (Node #0) to start communication.</li> <li>Test should wait for PLCA on all nodes to be activated before continuing with next step.</li> <li>Initiate data transmission with the respective PLCA Cycle and Message transfer.</li> <li>Measure the time between the expiration of one packet to the beginning of the next packet sent from the DUT with an oscilloscope (oscilloscope probe is connected at the MDI of the follower DUT), as shown as tmeasure in the figure below:</li> </ol>                                                                                                                                                                                                                                  |  |  |

Table 9: Main test structure of Group T3

| Instance<br>Test Case # | Description                                             | Parameter                                                                               | Condition                                                                                                 |

|-------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| TR3.1                   | PLCA Timing<br>requirements – Follower<br>Node - PACKET | TO_TIMER = minimum value declared by the PHY manufacturer <sup>5</sup> , 32, 36 and 40. | repeat the test with different values of the TO_TIMER and different values of the node ID/aPLCANodeCount. |

|                         |                                                         | Node_IDs = from 1 to 16                                                                 |                                                                                                           |

|                         |                                                         | The aPLCANodeCount should be incremented accordingly when Node_ID >1                    |                                                                                                           |

Table 10 - Test case instances definition for Group T3 - Tests case T3.1

RESTRICTION LEVEL: Public | June 16, 2025 | OPEN Alliance, Inc. Page | 26

<sup>&</sup>lt;sup>5</sup> **TO\_TIMER** = 28 will be considered if no minimum value is declared by the PHY manufacturer.

# 8.2 [D] PLCA Decoding of BEACON and message reception

# 8.2.1 Group D1 – Decoding of BEACON

| Durmaga             | The purpose of this test case is to test the ability of the DUT to correctly decode the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Purpose             | BEACON sent by the coordinator node.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |