# IEEE 100BASE-T1 Physical Coding Sublayer Test Suite

Version 1.1

| Author & Company  | Curtis Donahue, UNH-IOL                             |

|-------------------|-----------------------------------------------------|

|                   | Stephen Johnson, UNH-IOL                            |

| Title             | IEEE 100BASE-T1 Physical Coding Sublayer Test Suite |

| Version           | 1.1                                                 |

| Date              | August 3, 2017                                      |

| Status            | Final                                               |

| Restriction Level | Public                                              |

This suite of tests has been developed to help implementers evaluate the functionality of their 100BASE-T1 Physical Coding Sublayer (PCS) based products. This test suite covers both PCS Transmit and PCS Receive, including state diagrams, encoding/decoding, and scrambling/descrambling.

### **OPEN Alliance**

### Disclaimer

NOTICE TO USERS WHO ARE OPEN ALLIANCE SIG MEMBERS: Members of OPEN Alliance have the right to use and implement this Specification, subject to the Member's continued compliance with the OPEN Alliance SIG's goverance documents, Intellectual Property Rights Policy, and the applicable OPEN Alliance Promoter or Adopters Agreement. OPEN Specification documents may only be reproduced in electronic or paper form or utilized in order to achieve the Scope, as defined in the OPEN Alliance Intellectual Property Rights Policy. Reproduction or utilization for any other purposes as well as any modification of the Specification document, in any form or by any means, electronic or mechanical, including photocopying and microfilm, is explicitly excluded.

NOTICE TO NON-MEMBERS OF OPEN ALLIANCE SIG: If you are not a Member of OPEN Alliance and you have obtained a copy of this document, you only have a right to review this document for informational purposes. You do not have the right to reproduce, distribute, make derivative works of, publicly perform or publicly display this document in any way.

All OPEN Specifications are provided on an "as is" basis and all warranties, either explicit or implied, are excluded unless mandatory under law. Accordingly, the OPEN Alliance Members who have contributed to the OPEN Specifications make no representations or warranties with regard to the OPEN Specifications or the information (including any software) contained therein, including any warranties of merchantability, fitness for purpose, or absence of third party rights and make no representations as to the accuracy or completeness of the OPEN Specifications or any information contained therein.

The OPEN Alliance Members who have contributed to the OPEN Specifications will not be liable for any losses, costs, expenses or damages arising in any way out of use or reliance upon any OPEN Specification or any information therein. Nothing in this document operates to limit or exclude any liability for fraud or any other liability which is not permitted to be excluded or limited by operation of law.

The material contained in OPEN Specifications is protected by copyright and may be subject to other types of Intellectual Property Rights.

The distribution of OPEN Specifications shall not operate as an assignment or license to any recipient of any OPEN Specification of any patents, registered designs, unregistered designs, trademarks, trade names or other rights as may subsist in or be contained in or reproduced in any OPEN Specification. The commercial exploitation of the material in this document may require such a license, and any and all liability arising out of use without such a license is excluded.

Without prejudice to the foregoing, the OPEN Alliance Specifications have been developed for automotive applications only. They have neither been developed, nor tested for non-automotive applications.

OPEN Alliance reserves the right to withdraw, modify, or replace any OPEN Specification at any time, without notice.

# **Version Control of Document**

| Version      | Author             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          | Date      |

|--------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1.0          | Stephen<br>Johnson | <ul> <li>Document updated to reference IEEE 802.3bw 100BASE-T1 Standard.</li> <li>Updated observable result for Test 3.4.8 – Receive State Diagram - THIRD SSD State part b.</li> </ul>                                                                                                                                                                                                                                                              | 06/9/2016 |

| 1.1          | Stephen<br>Johnson | <ul> <li>Updated reference table</li> <li>Updated references and procedure for Test 3.1.1 – PCS         Signaling</li> <li>Updated discussion and procedure for Test 3.1.2 – PCS         Reset</li> <li>Updated references for Test 3.1.3 – Transmit Proper SSD,         Test 3.1.4 – Transmit Proper ESD, Test 3.1.5 – Transmit ESD         with tx_error, Test 3.1.7 – tx_error, Test 3.5.1 – JAB State         Diagram – rcv_max_timer</li> </ul> |           |

| 1.0_Internal | Stephen<br>Johnson | <ul> <li>Updated version number to 1.0_Internal</li> <li>Removed UNH IOL disclaimer</li> <li>Removed references to UNH IOL</li> <li>Updated Appendix 3.C – Line Tap</li> <li>Removed last updated section from each test</li> </ul>                                                                                                                                                                                                                  | 5/4/17    |

| 1.0          | Stephen<br>Johnson | <ul><li>Draft finalized</li><li>Restriction level changed to Public</li></ul>                                                                                                                                                                                                                                                                                                                                                                        | 6/6/17    |

| 1.1          | Stephen<br>Johnson | Removed second restriction level table                                                                                                                                                                                                                                                                                                                                                                                                               | 8/3/17    |

# Restriction level history of Document

| Version      | Restriction Level  | Description | Date      |

|--------------|--------------------|-------------|-----------|

| 1.0          | OPEN internal only |             | 06/9/2016 |

| 1.1          | OPEN internal only |             | 3/2/2017  |

| 1.0_Internal | OPEN internal only |             | 5/4/17    |

| 1.0          | Public             |             | 6/6/17    |

| 1.1          | Public             |             | 8/3/17    |

# **OPEN Alliance**

# **Contents**

| 1 | A    | CKNOWLEDGMENTS                                                               | 6  |  |

|---|------|------------------------------------------------------------------------------|----|--|

| 2 | IN   | INTRODUCTION                                                                 |    |  |

| 3 | R    | eference Table                                                               | 9  |  |

| 4 | D    | evice Under Test (DUT) Requirements                                          | 11 |  |

| 5 | G    | ROUP 1: PCS Transmit                                                         | 12 |  |

|   | 5.1  | Test 3.1.1 – PCS Signaling                                                   | 13 |  |

|   | 5.2  | Test 3.1.2 – PCS Reset                                                       | 15 |  |

|   | 5.3  | Test 3.1.3 – Transmit Proper SSD                                             | 16 |  |

|   | 5.4  | Test 3.1.4 – Transmit Proper ESD                                             | 17 |  |

|   | 5.5  | Test 3.1.5 – Transmit ESD with tx_error                                      | 18 |  |

|   | 5.6  | Test 3.1.6 – Transmission of Stuff Bits                                      | 19 |  |

|   | 5.7  | Test 3.1.7 – tx_error                                                        | 20 |  |

| 6 | G    | ROUP 2: PCS Transmit State Diagram                                           | 22 |  |

|   | 6.1  | Test 3.2.1 – PCS Transmit State Diagram - SEND IDLE State                    | 23 |  |

|   | 6.2  | Test 3.2.2 – PCS Transmit State Diagram - SSD1 VECTOR and SSD2 VECTOR states | 24 |  |

|   | 6.3  | Test 3.2.3 – PCS Transmit State Diagram - SSD3 VECTOR state                  | 25 |  |

|   | 6.4  | Test 3.2.4 – PCS Transmit State Diagram - TRANSMIT DATA state                | 27 |  |

|   | 6.5  | Test 3.2.5 – PCS Transmit State Diagram - ESD1 VECTOR state                  | 29 |  |

|   | 6.6  | Test 3.2.6 – PCS Transmit State Diagram - ESD2 VECTOR state                  | 30 |  |

|   | 6.7  | Test 3.2.7 – PCS Transmit State Diagram - ESD3 VECTOR state                  | 31 |  |

|   | 6.8  | Test 3.2.8 – PCS Transmit State Diagram - ERR ESD1 VECTOR state              | 32 |  |

|   | 6.9  | Test 3.2.9 – PCS Transmit State Diagram - ERR ESD2 VECTOR state              | 33 |  |

|   | 6.10 | Test 3.2.10 – PCS Transmit State Diagram - ERR ESD3 VECTOR state             | 34 |  |

| 7 | G    | ROUP 3: PCS Receive                                                          | 35 |  |

|   | 7.1  | Test 3.3.1 – Receive PCS Signaling.                                          | 36 |  |

|   | 7.2  | Test 3.3.2 – Automatic Polarity Detection (Optional)                         | 37 |  |

|   | 7.3  | Test 3.3.3 – Receive SSD                                                     | 38 |  |

|   | 7.4  | Test 3.3.4 – Receive ESD.                                                    | 39 |  |

|   | 7.5  | Test 3.3.5 – Receive ERR_ESD3                                                | 40 |  |

|   | 7.6  | Test 3.3.6 – Reception of Stuff Bits                                         | 41 |  |

|   | 7.7  | Test 3.3.7 – De-Interleave Ternary Pairs.                                    | 42 |  |

# **OPEN Alliance**

| 8  | GI   | ROUP 4: PCS Receive State Diagram                                 | 43 |

|----|------|-------------------------------------------------------------------|----|

|    | 8.1  | Test 3.4.1 – Receive State Diagram - IDLE State                   | 44 |

|    | 8.2  | Test 3.4.2 – Receive State Diagram - CHECK SSD2 State             | 45 |

|    | 8.3  | Test 3.4.3 – Receive State Diagram - CHECK SSD3 State             | 46 |

|    | 8.4  | Test 3.4.4 – Receive State Diagram - SSD State                    | 47 |

|    | 8.5  | Test 3.4.5 – Receive State Diagram - BAD SSD State                | 48 |

|    | 8.6  | Test 3.4.6 – Receive State Diagram - FIRST SSD State              | 50 |

|    | 8.7  | Test 3.4.7 – Receive State Diagram - SECOND SSD State             | 51 |

|    | 8.8  | Test 3.4.8 – Receive State Diagram - THIRD SSD State              | 52 |

|    | 8.9  | Test 3.4.9 – Receive State Diagram - DATA State                   | 53 |

|    | 8.10 | Test 3.4.10 – Receive State Diagram - CHECK ESD2 State            | 54 |

|    | 8.11 | Test 3.4.11 – Receive State Diagram - CHECK ESD3 State            | 55 |

|    | 8.12 | Test 3.4.12 – Receive State Diagram - BAD ESD2 State              | 56 |

|    | 8.13 | Test 3.4.13 – Receive State Diagram - BAD END and RX ERROR states | 57 |

| 9  | GI   | ROUP 5: JAB State Diagram                                         | 58 |

|    | 9.1  | Test 3.5.1 – JAB State Diagram - rcv_max_timer                    | 59 |

| 10 | ) .  | TEST SUITE APPENDICES                                             | 60 |

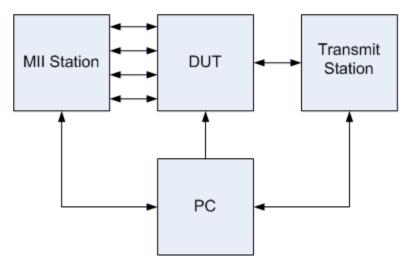

|    | 10.1 | Appendix 3.A –Testing Devices Without MII Access                  | 61 |

|    | 10.2 | Appendix 3.B – Test Stations                                      | 70 |

|    | 10.3 | Annendix 3 C – Line Tan                                           | 72 |

# 1 ACKNOWLEDGMENTS

The OPEN Alliance would like to acknowledge the efforts of the following individuals in the development of this test suite.

**Curtis Donahue** University of New Hampshire **Dave Estes** University of New Hampshire University of New Hampshire Stephen Johnson Matt Kilpeck University of New Hampshire University of New Hampshire Shawn King Jeff Lapak University of New Hampshire Matt Mayer University of New Hampshire **Alex Seiger** University of New Hampshire

# 2 INTRODUCTION

This particular suite of tests has been developed to help implementers evaluate the functionality of the PCS sublayer of their 100BASE-T1 products.

These tests are designed to determine if a product conforms to specifications defined in IEEE 802.3bw 100BASE-T1 Standard. Successful completion of all tests contained in this suite does not guarantee that the tested device will operate with other devices. However, combined with satisfactory operation in the OPEN Alliance interoperability test bed, these tests provide a reasonable level of confidence that the Device Under Test (DUT) will function properly in many 100BASE-T1 automotive environments.

The tests contained in this document are organized in such a manner as to simplify the identification of information related to a test, and to facilitate in the actual testing process. Tests are organized into groups, primarily in order to reduce setup time in the lab environment, however the different groups typically also tend to focus on specific aspects of device functionality. A three-part numbering system is used to organize the tests, where the first number indicates the section of Clause 96 of the IEEE 802.3bw Standard on which the test suite is based. The second and third numbers indicate the test's group number and test number within that group, respectively. This format allows for the addition of future tests to the appropriate groups without requiring the renumbering of the subsequent tests.

The test definitions themselves are intended to provide a high-level description of the motivation, resources, procedures, and methodologies pertinent to each test. Specifically, each test description consists of the following sections:

### **Purpose**

The purpose is a brief statement outlining what the test attempts to achieve. The test is written at the functional level.

### References

This section specifies source material *external* to the test suite, including specific subsections pertinent to the test definition, or any other references that might be helpful in understanding the test methodology and/or test results. External sources are always referenced by number when mentioned in the test description. Any other references not specified by number are stated with respect to the test suite document itself.

### **Resource Requirements**

The requirements section specifies the test hardware and/or software needed to perform the test. This is generally expressed in terms of minimum requirements, however in some cases specific equipment manufacturer/model information may be provided.

### **Last Modification**

This specifies the date of the last modification to this test.

### Discussion

The discussion covers the assumptions made in the design or implementation of the test, as well as known limitations. Other items specific to the test are covered here.

# Test Setup

### **OPEN Alliance**

The setup section describes the initial configuration of the test environment. Small changes in the configuration should not be included here, and are generally covered in the test procedure section, below.

### **Test Procedure**

The procedure section of the test description contains the systematic instructions for carrying out the test. It provides a cookbook approach to testing, and may be interspersed with observable results.

### **Observable Results**

This section lists the specific observables that can be examined by the tester in order to verify that the DUT is operating properly. When multiple values for an observable are possible, this section provides a short discussion on how to interpret them. The determination of a pass or fail outcome for a particular test is generally based on the successful (or unsuccessful) detection of a specific observable.

### **Possible Problems**

This section contains a description of known issues with the test procedure, which may affect test results in certain situations. It may also refer the reader to test suite appendices and/or whitepapers that may provide more detail regarding these issues.

# 3 Reference Table

| Test Name                    |                    | IEEE 802.3bw References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | Test Number        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                              | Grou               | p 1: PCS Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PCS Signaling                | Test 3.1.1         | <ul> <li>[1] IEEE Std. 802.3bw subclause 96.3.3.1 – 4B/3B conversion</li> <li>[2] IEEE Std. 802.3bw subclause 96.3.3.3.1 – Side-stream scrambler polynomial</li> <li>[3] IEEE Std. 802.3bw subclause 96.3.3.3.2 – Generation of Syn[2:0]</li> <li>[4] IEEE Std. 802.3bw subclause 96.3.3.3.3 – Generation of Scn[2:0]</li> <li>[5] IEEE Std. 802.3bw subclause 96.3.3.3.4 – Generation of scrambled bits Sdn[2:0]</li> <li>[6] IEEE Std. 802.3bw subclause 96.3.3.3.5 – Generation of ternary pair (TA<sub>n</sub>, TB<sub>n</sub>)</li> <li>[7] IEEE Std. 802.3bw table 96-1 – Idle symbol mapping in training</li> <li>[8] IEEE Std. 802.3bw table 96-2 – Data symbols when tx_mode=SEND_N</li> <li>[9] IEEE Std. 802.3bw table 96-3 – Idle symbols when tx_mode=SEND_N</li> </ul> |

| PCS Reset                    | Test 3.1.2         | [1] IEEE Std. 802.3bw subclause 96.3.1 – PCS Reset function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Transmit Proper SSD          | Test 3.1.3         | <ul> <li>[1] IEEE Std. 802.3bw subclause 96.3.3 – PCS transmit</li> <li>[2] IEEE Std. 802.3bw subclause 96.3.3.3.5 – Generation of ternary pair (TA<sub>n</sub>, TB<sub>n</sub>)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Transmit Proper ESD          | Test 3.1.4         | <ul> <li>[1] IEEE Std. 802.3bw subclause 96.3.3 – PCS transmit</li> <li>[2] IEEE Std. 802.3bw subclause 96.3.3.3.5 – Generation of ternary pair (TA<sub>n</sub>, TB<sub>n</sub>)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Transmit ESD with tx_error   | Test 3.1.5         | <ul> <li>[1] IEEE Std. 802.3bw subclause 96.3.3 – PCS transmit</li> <li>[2] IEEE Std. 802.3bw subclause 96.3.3.3.5 – Generation of ternary pair (TA<sub>n</sub>, TB<sub>n</sub>)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Transmission of Stuff Bits   | Test 3.1.6         | • [1] IEEE Std. 802.3bw subclause 96.3.3.1.2 –4B/3B conversion for MII data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| tx_error                     | Test 3.1.7         | <ul> <li>[1] IEEE Std. 802.3bw subclause 96.3.3 – PCS transmit</li> <li>[2] IEEE Std. 802.3bw Figure 96-6: 4B3B MII Signal Conversion</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              | Group 2: PCS       | Transmit State Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Transmit State Diagram       | Tests 3.2.1-3.2.10 | • [1] IEEE Std. 802.3bw figure 96-7 – PCS Transmit state diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              | Grou               | up 3: PCS Receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Receive PCS Signaling        | Test 3.3.1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Automatic Polarity Detection | Test 3.3.2         | [1] IEEE Std. 802.3bw subclause 96.3.4 – PCS Receive     [1] IEEE Std. 802.3bw subclause 96.3.4.4 – PCS Receive automatic polarity detection (optional)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Receive SSD                  | Test 3.3.3         | [1] IEEE Std. 802.3bw figure 96-10 – PCS Receive state diagram     [1] IEEE Std. 802.3bw subclause 96.3.4.2 – PCS Receive symbol decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Receive ESD                  | Test 3.3.4         | <ul> <li>[1] IEEE Std. 802.3bw figure 96-10 – PCS Receive state diagram</li> <li>[1] IEEE Std. 802.3bw subclause 96.3.4.2 – PCS Receive symbol decoding</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Receive ERR_ESD3             | Test 3.3.5         | <ul> <li>[1] IEEE Std. 802.3bw figure 96-10 – PCS Receive state diagram</li> <li>[1] IEEE Std. 802.3bw subclause 96.3.4.2 – PCS Receive symbol decoding</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Reception of Stuff Bits      | Test 3.3.6         | [1] IEEE Std. 802.3bw subclause 96.3.4.2 – PCS Receive symbol decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# **OPEN Alliance**

| De-Interleave Ternary Pairs        | Test 3.3.7         | [1] IEEE std. 802.3bw subclause 96.3.4.2 PCS Receive symbol decoding                                                                                                                                           |  |

|------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Group 4: PCS Receive State Diagram |                    |                                                                                                                                                                                                                |  |

| Receive State Diagram              | Tests 3.4.1-3.4.13 | • [1] IEEE Std. 802.3bw figure 96-10 – PCS Receive state diagram                                                                                                                                               |  |

| Group 5: JAB State Diagram         |                    |                                                                                                                                                                                                                |  |

| JAB State Diagram - rcv_max_timer  | Test 3.5.1         | <ul> <li>[1] IEEE Std. 802.3bw figure 96-11 – JAB state diagram</li> <li>[1] IEEE Std. 802.3bw figure 96-10 – PCS Receive state diagram</li> <li>[2] IEEE Std. 802.3bw subclause 96.3.4.1.3 – Timer</li> </ul> |  |

All tests are designed for the IEEE 802.3bw 100BASE-T1 Standard.

# 4 Device Under Test (DUT) Requirements

For the purposes of this test suite, a DUT is one port of a 100BASE-T1 capable device that includes a 100BASE-T1 PHY mounted on a PCB and an MDI connector. Please see the additional requirements listed in the following table:

| Test Number and Name                      | Required Capabilities                               |

|-------------------------------------------|-----------------------------------------------------|

|                                           |                                                     |

| General                                   | The Ability to send and receive frames <sup>1</sup> |

|                                           |                                                     |

| Test 3.1.2 – PCS Reset                    | Access to PCS Reset                                 |

| Test 3.1.5 – Transmit ESD with tx_error   | MII Access                                          |

| Test 3.1.7 – tx_error                     | MII Access                                          |

|                                           | MII Access                                          |

| GROUP 2: PCS Transmit State Diagram       |                                                     |

| Test 3.3.2 – Automatic Polarity Detection | The DUT must implement Automatic Polarity           |

| (Optional)                                | Detection                                           |

| GROUP 4: PCS Receive State Diagram        | MII Access                                          |

| GROUP 5: JAB State Diagram                | MII Access                                          |

<sup>1)</sup> This can be accomplished through a loopback, responding to ICMP requests, or by forwarding traffic through two ports.

# 5 GROUP 1: PCS Transmit

# Overview:

The tests defined in this section verify the PCS Transmit process defined for 100BASE-T1 capable PHYs in sections 96.3.1 and 96.3.3 of the IEEE 802.3bw 100BASE-T1 Specification.

# 5.1 Test 3.1.1 - PCS Signaling

**Purpose:** To verify that the PCS properly performs the 4B/3B conversion, side-stream scrambling, and ternary symbol generation.

### References:

- [1] IEEE Std. 802.3bw subclause 96.3.3.1 4B/3B conversion

- [2] IEEE Std. 802.3bw subclause 96.3.3.3.1 Side-stream scrambler polynomial

- [3] IEEE Std. 802.3bw subclause 96.3.3.3.2 Generation of Syn[2:0]

- [4] IEEE Std. 802.3bw subclause 96.3.3.3.3 Generation of Scn[2:0]

- [5] IEEE Std. 802.3bw subclause 96.3.3.3.4 Generation of scrambled bits Sdn[2:0]

- [6] IEEE Std. 802.3bw subclause 96.3.3.3.5 Generation of ternary pair (TA<sub>n</sub>, TB<sub>n</sub>)

- [7] IEEE Std. 802.3bw table 96-1 Idle symbol mapping in training

- [8] IEEE Std. 802.3bw table 96-2 Data symbols when TXMODE=SEND\_N

- [9] IEEE Std. 802.3bw table 96-3 Idle symbols when TXMODE=SEND\_N

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A compliant 100BASE-T1 Link Partner

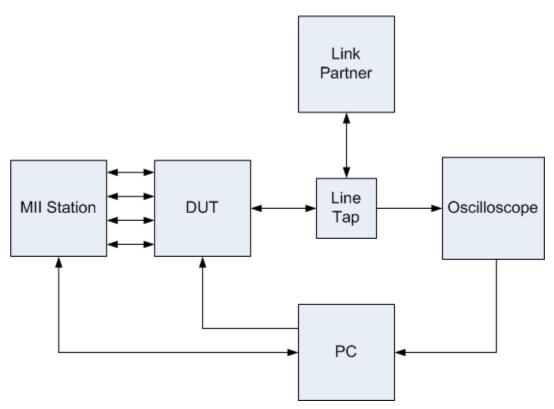

- A line tap (Refer to appendix 3.C)

### Discussion:

The 100BASE-T1 PCS uses a combination of a 4B3B conversion for MII data, side-stream scrambling, and ternary symbols to encode the data for transmission on the line. In addition to the scrambler, there are additional functions performed on the data and idle streams to eliminate the correlation transmit data and to balance the power density.

This test is designed to ensure that the DUT properly performs the 100BAE-T1 encoding during training, idle transmission, and data transmission.

**Test Setup:** Connect the Device Under Test (DUT) to the Link Partner via the line tap.

### **Test Procedure:**

- 1. Configure the DUT as master and the Link Partner as slave.

- 2. Monitor and decode the transmissions from the DUT while the DUT is in tx mode = SEND I.

- 3. Monitor and decode the transmissions from the DUT while the DUT is in tx\_mode = SEND\_N and tx\_enable = 1.

- 4. Monitor and decode the transmissions from the DUT while the DUT is in tx\_mode = SEND\_N and tx\_enable = 0.

- 5. Configure the DUT as slave and the Link Partner as master.

- 6. Monitor and decode the transmissions from the DUT while the DUT is in tx mode = SEND I.

- 7. Monitor and decode the transmissions from the DUT while the DUT is in tx\_mode = SEND\_N and tx\_enable = 1.

- 8. Monitor and decode the transmissions from the DUT while the DUT is in tx\_mode = SEND\_N and tx\_enable = 0.

### **Observable Results:**

- a. The transmissions in Step 2 should follow the 4B3B conversion specified in [1], the side-stream scrambler polynomial specified in [2] for master, the generation of Sdn[2:0] specified in [5], and the ternary symbol mapping defined in [6].

- b. The transmissions in Step 3 should follow the 4B3B conversion specified in [1], the side-stream scrambler polynomial specified in [2] for master, the generation of Sdn[2:0] specified in [5], and the ternary symbol mapping defined in [8].

- c. The transmissions in Step 4 should follow the 4B3B conversion specified in [1], the side-stream scrambler polynomial specified in [2] for master, the generation of Sdn[2:0] specified in [5], and the ternary symbol mapping defined in [9].

- d. The transmissions in Step 6 should follow the 4B3B conversion specified in [1], the side-stream scrambler polynomial specified in [2] for master, the generation of Sdn[2:0] specified in [5], and the ternary symbol mapping defined in [6].

- e. The transmissions in Step 7 should follow the 4B3B conversion specified in [1], the side-stream scrambler polynomial specified in [2] for master, the generation of Sdn[2:0] specified in [5], and the ternary symbol mapping defined in [8].

- f. The transmissions in Step 8 should follow the 4B3B conversion specified in [1], the side-stream scrambler polynomial specified in [2] for master, the generation of Sdn[2:0] specified in [4], and the ternary symbol mapping defined in [9].

Possible Problems: Some devices may not allow configuration as master or slave, in which case only the supported configuration will be tested.

### **5.2** Test **3.1.2** - PCS Reset

Purpose: To verify that the PCS properly initializes upon receipt of a reset request from the management entity.

### References:

[1] IEEE Std. 802.3bw subclause 96.3.1 – PCS Reset function

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

### Discussion:

Reference [1] states that the PCS is reset upon power on or the receipt of a reset request from management entity. The PCS Reset function causes the PCS Transmit State Diagram to transition to the SEND IDLE state and the side-stream scrambler to be reset. The initial value of the scrambler shall never be all zeros.

**Test Setup:** Connect the Device Under Test (DUT) to the Link Partner via the line tap.

### Procedure:

- 1. Configure the DUT as master.

- 2. Monitor and decode the transmissions from the DUT and cause the management to request a PCS Reset.

- 3. Configure the DUT as slave and repeat step 2.

### **Observable Results:**

- a. The DUT should transition to the SEND IDLE state upon reception of a PCS Reset request when configured as master.

- b. The DUT should transition to the SEND IDLE state upon reception of a PCS Reset request when configured as slave.

- c. The DUT should reset the scrambler to a non-zero value upon reception of a PCS Reset request when configured as master.

- d. The DUT should reset the scrambler to a non-zero value upon reception of a PCS Reset request when configured as slave.

Possible Problems: If the ability to control the PCS Reset request is not available, this test cannot be performed. Also, some devices may not allow configuration as master or slave, in which case only the supported configuration will be tested.

# 5.3 Test 3.1.3 - Transmit Proper SSD

**Purpose:** To verify that the PCS properly transmits the SSD upon assertion of tx\_enable.

### References:

[1] IEEE Std. 802.3bw subclause 96.3.3 – PCS transmit

[2] IEEE Std. 802.3bw subclause 96.3.3.3.5 – Generation of ternary symbol (TA<sub>n</sub>, TB<sub>n</sub>)

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

### Discussion:

Reference [1] states that the PCS transmits 6 consecutive systems of SSD to the PMA upon assertion of  $tx_e$  enable. Reference [2] states that this translates to ternary symbols of (0,0), (0,0), (0,0).

**Test Setup:** Connect the Device Under Test (DUT) to the Link Partner via the line tap.

### Procedure:

1. Monitor and decode the transmissions from the DUT as the DUT is sending frames.

### Observable Results:

a. The DUT should transmit (0,0), (0,0), (0,0) at the beginning of every frame.

Possible Problems: None.

# 5.4 Test 3.1.4 - Transmit Proper ESD

**Purpose:** To verify that the PCS properly transmits the ESD upon de-assertion of tx\_enable in the absence of a transmit error.

### References:

[1] IEEE Std. 802.3bw subclause 96.3.3 – PCS transmit [2] IEEE Std. 802.3bw subclause 96.3.3.5 – Generation of ternary symbol (TA<sub>n</sub>, TB<sub>n</sub>)

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

### Discussion:

Reference [1] states that the PCS transmits 6 consecutive systems of ESD to the PMA upon de-assertion of  $tx_e$  nable in the absence of transmit errors. Reference [2] states that this translates to ternary symbols of (0,0), (0,0), (1,1).

**Test Setup:** Connect the Device Under Test (DUT) to the Link Partner via the line tap.

### Procedure:

1. Monitor and decode the transmissions from the DUT as the DUT is sending frames.

### **Observable Results:**

a. The DUT should transmit (0,0), (0,0), (1,1) at the end of every frame that does not have transmit errors.

Possible Problems: None.

# 5.5 Test 3.1.5 - Transmit ESD with tx\_error

**Purpose:** To verify that the PCS properly transmits the ESD\_err upon de-assertion of tx\_enable in the presence of a transmit error.

### References:

[1] IEEE Std. 802.3bw subclause 96.3.3 – PCS transmit [2] IEEE Std. 802.3bw subclause 96.3.3.5 – Generation of ternary symbol (TA<sub>n</sub>, TB<sub>n</sub>)

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

### Discussion:

Reference [1] states that the PCS transmits 6 consecutive systems of ESD\_err to the PMA upon deassertion of  $tx_e$  assertion of  $tx_e$  and  $tx_e$  that this translates to ternary symbols of (0,0), (0,0), (-1,-1).

**Test Setup:** Connect the Device Under Test (DUT) to the Link Partner via the line tap.

### Procedure:

1. Monitor and decode the transmissions from the DUT as the DUT is sending frames while causing the DUT to send transmit errors.

### **Observable Results:**

a. The DUT should transmit (0,0), (0,0), (-1,-1) at the end of every frame that has a transmit error.

**Possible Problems:** It will not be possible to perform this test if there is no method to force the DUT to transmit a frame with a transmit error. This can be accomplished through an MII test station if there is direct access to the MII.

### 5.6 Test 3.1.6 - Transmission of Stuff Bits

Purpose: To verify that the PCS inserts stuff bits during the 4B3B conversion for MII data.

### References:

[1] IEEE Std. 802.3bw subclause 96.3.3.1.2 – 4B3B conversion for MII data

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

### Discussion:

Reference [1] states that the DUT shall append stuff bits at the end of every packet that is not a multiple of 3 bits in length.

**Test Setup:** Connect the Device Under Test (DUT) to the Link Partner via the line tap.

### Procedure:

- 1. Monitor and decode the transmissions from the DUT as the DUT is sending frames of several lengths that are a multiple of 3 (when including 8 bytes for preamble), including but not limited to 64 bytes and 67 bytes.

- 2. Monitor and decode the transmissions from the DUT as the DUT is sending frames of several lengths that are 1 more than a multiple of 3 (when including 8 bytes for preamble), including but not limited to 66 bytes and 69 bytes.

- 3. Monitor and decode the transmissions from the DUT as the DUT is sending frames of several lengths that are 2 more than a multiple of 3 (when including 8 bytes for preamble), including but not limited to 65 bytes and 68 bytes.

### Observable Results:

- a. In step 1 the DUT should not transmit stuff bits.

- b. In step 2 the DUT should transmit 2 stuff bits.

- c. In step 3 the DUT should transmit 1 stuff bit.

Possible Problems: None.

### 5.7 Test 3.1.7 - tx error

**Purpose:** To verify that the PCS properly sets tx\_error based on the value of tx\_error\_mii and tx\_enable\_mii.

### References:

- [1] IEEE Std. 802.3bw subclause 96.3.3 PCS Transmit

- [2] IEEE Std. 802.3bw Figure 96-6: 4B3B MII signal conversion

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A test station capable of controlling the MII signals

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

### Discussion:

Reference [1] states that the DUT shall set tx\_error=TRUE if tx\_error\_mii is asserted during the packet period. References [1] and [2] indicate that tx\_error=TRUE is held until the DUT enters the ERR ESD1 VECTOR state.

**Test Setup:** Connect the Device Under Test (DUT) to the Link Partner via the line tap.

### Procedure:

- 1. Configure the test station and Link Partner such that the DUT establishes a valid link while the MII station is sending TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE.

- 2. Instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=TRUE for 1 clock cycle, then set TXD=0101, TX\_EN=TRUE, and TX\_ER=FALSE for 5 clock cycles, and then set TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE for at least 2 clock cycles.

- 3. Monitor the transmissions from the DUT.

- Repeat steps 1-3, except instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=FALSE for 7 clock cycles, then set TXD=0000, TX\_EN=TRUE, and TX\_ER=TRUE for 1 clock cycle, and then set TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE for at least 3 clock cycles in step

- 5. Repeat steps 1-3, except instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=FALSE for 6 clock cycles, then set TXD=0000, TX\_EN=FALSE, and TX\_ER=TRUE for at least 2 clock cycles in step 2.

- Repeat steps 1-3, except instruct the MII station to set TXD=0000, TX\_EN=FALSE, and TX\_ER=TRUE for 1 clock cycle, then set TXD=0101, TX\_EN=TRUE, and TX\_ER=FALSE for 6 clock cycles, and then set TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE for at least 2 clock cycles in step 2.

### Observable Results:

- a. In step 2, after exiting the TRANSMIT DATA state, the DUT should transmit ESD1, ESD2, and ERR\_ESD3.

- b. In step 4, after exiting the TRANSMIT DATA state, the DUT should transmit ESD1, ESD2, and ERR\_ESD3.

- c. In step 5, after exiting the TRANSMIT DATA state, the DUT should transmit ESD1, ESD2, and ESD3.

# **OPEN Alliance**

d. In step 6, after exiting the TRANSMIT DATA state, the DUT should transmit ESD1, ESD2, and ESD3

Possible Problems: None.

# 6 GROUP 2: PCS Transmit State Diagram

# Overview:

The tests defined in this section verify the PCS Transmit State Diagram defined for 100BASE-T1 capable PHYs in section 96.3.3.2 of the IEEE 802.3bw 100BASE-T1 Specification.

# 6.1 Test 3.2.1 - PCS Transmit State Diagram - SEND IDLE State

Purpose: To verify that the DUT properly behaves while in the SEND IDLE state.

### References:

[1] IEEE Std. 802.3bw figure 96-7 – PCS Transmit state diagram

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A test station capable of controlling the MII signals

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

### Discussion:

Reference [1] shows the valid transitions that a 100BASE-T1 device can take through the PCS Transmit State Diagram. The DUT should remain in the SEND IDLE state until tx enable=TRUE.

Test Setup: Connect the MII of the Device Under Test (DUT) to the MII test station and the 100BASE-T1 interface of the DUT to the Link Partner via the line tap.

### Procedure:

- 1. Configure the test station and Link Partner such that the DUT establishes a valid link while the MII station is sending TXD=0, TX EN=FALSE, and TX ER=FALSE.

- 2. Instruct the MII station to send frame data on TXD while keeping TX\_EN=FALSE.

- 3. Monitor the transmissions from the DUT.

- 4. Repeat steps 1-3, except instruct the MII station to set TX ER=TRUE in step 2.

- 5. Repeat steps 1-3, except instruct the MII station to set TX ER=FALSE and TX EN=TRUE in step 2.

- 6. Repeat steps 1-3, except instruct the MII station to set TX ER=TRUE and TX EN=TRUE in step 2.

### **Observable Results:**

- a. In step 2, the DUT should remain in the SEND IDLE state.

- b. In step 4, the DUT should remain in the SEND IDLE state.

- c. In step 5, the DUT should transition to the SSD1 VECTOR state and transmit SSD1.

- d. In step 6, the DUT should transition to the SSD1 VECTOR state and transmit SSD1.

# 6.2 Test 3.2.2 - PCS Transmit State Diagram - SSD1 VECTOR and SSD2 VECTOR states

Purpose: To verify that the DUT properly behaves while in the SSD1 VECTOR and SSD2 VECTOR states.

### References:

[1] IEEE Std. 802.3bw figure 96-7 – PCS Transmit state diagram

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A test station capable of controlling the MII signals

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

### Discussion:

Reference [1] shows the valid transitions that a 100BASE-T1 device can take through the PCS Transmit State Diagram. Regardless of the transmissions on the MII, once the DUT enters the SSD1 VECTOR state the DUT should transmit SSD1, immediately transition to the SSD2 VECTOR state, transmit SSD2, and then immediately transition to the SSD3 VECTOR state.

**Test Setup:** Connect the MII of the Device Under Test (DUT) to the MII test station and the 100BASE-T1 interface of the DUT to the Link Partner via the line tap.

### Procedure:

- 1. Configure the test station and Link Partner such that the DUT establishes a valid link while the MII station is sending TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE.

- 2. Instruct the MII station to set TX EN=TRUE and TX ER=FALSE for at least 3 clock cycles.

- 3. Monitor the transmissions from the DUT.

- 4. Repeat steps 1-3, except instruct the MII station to set TX\_EN=TRUE and TX\_ER=TRUE for at least 3 clock cycles in step 2.

- 5. Repeat steps 1-3, except instruct the MII station to set TX\_EN=TRUE and TX\_ER=FALSE for 1 clock cycle, and then set TX\_EN=TRUE and TX\_ER=TRUE for at least 2 clock cycles in step 2.

- 6. Repeat steps 1-3, except instruct the MII station to set TX\_EN=TRUE and TX\_ER=FALSE for 1 clock cycle, then set TX\_EN=FALSE and TX\_ER=FALSE in step 2.

- 7. Repeat steps 1-3, instruct the MII station to set TX\_EN=TRUE and TX\_ER=FALSE for 1 clock cycle, then set TX\_EN=FALSE and TX\_ER=TRUE in step 2.

# **Observable Results:**

- a. In step 2, the DUT should transmit SSD1, SSD2, and SSD3.

- b. In step 4, the DUT should transmit SSD1, SSD2, and SSD3.

- c. In step 5, the DUT should transmit SSD1, SSD2, and SSD3.

- d. In step 6, the DUT should transmit SSD1, SSD2, and SSD3.

- e. In step 7, the DUT should transmit SSD1, SSD2, and SSD3.

# 6.3 Test 3.2.3 - PCS Transmit State Diagram - SSD3 VECTOR state

**Purpose:** To verify that the DUT properly behaves while in the SSD3 VECTOR state.

### References:

[1] IEEE Std. 802.3bw figure 96-7 – PCS Transmit state diagram

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A test station capable of controlling the MII signals

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

### Discussion:

Reference [1] shows the valid transitions that a 100BASE-T1 device can take through the PCS Transmit State Diagram. Once the DUT enters the SSD3 VECTOR state, the DUT should transmit SSD3 and then transition to TRANSMIT DATA, ERR ESD1 VECTOR, or ESD1 VECTOR.

**Test Setup:** Connect the MII of the Device Under Test (DUT) to the MII test station and the 100BASE-T1 interface of the DUT to the Link Partner via the line tap.

### **Procedure:**

- 1. Configure the test station and Link Partner such that the DUT establishes a valid link while the MII station is sending TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE.

- 2. Instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=FALSE for at least 3 clock cycles.

- 3. Monitor the transmissions from the DUT.

- 4. Repeat steps 1-3, except instruct the MII station to set TXD=0000, TX\_EN=TRUE and TX\_ER=FALSE for at least 3 clock cycles in step 2.

- 5. Repeat steps 1-3, except instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=FALSE for 2 clock cycles, and then set TX\_EN=TRUE and TX\_ER=TRUE for at least 1 clock cycle in step 2.

- 6. Repeat steps 1-3, except instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=FALSE for 2 clock cycles, then set TX\_EN=FALSE and TX\_ER=FALSE for at least 4 clock cycles in step 2.

- 7. Repeat steps 1-3, except instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=TRUE for 2 clock cycles, then set TX\_EN=FALSE and TX\_ER=FALSE for at least 4 clock cycles in step 2.

# **Observable Results:**

- a. In step 2, the DUT should transmit SSD1 and SSD2, enter the SSD3 VECTOR state and transmit SSD3, and then enter the TRANSMIT DATA state and transmit the scrambled version of "010".

- b. In step 4, the DUT should transmit SSD1 and SSD2, enter the SSD3 VECTOR state and transmit SSD3, and then enter the TRANSMIT DATA state and transmit the scrambled version of "000".

- c. In step 5, the DUT should transmit SSD1 and SSD2, enter the SSD3 VECTOR state and transmit SSD3, and then enter the TRANSMIT DATA state and transmit the scrambled version of "010".

- d. In step 6, the DUT should transmit SSD1 and SSD2, enter the SSD3 VECTOR state and transmit SSD3, enter the ESD1 VECTOR state and transmit ESD1, and then transmit ESD2 and ESD3.

### **OPEN Alliance**

e. In step 7, the DUT should transmit SSD1 and SSD2, enter the SSD3 VECTOR state and transmit SSD3, enter the ERR ESD1 VECTOR state and transmit ESD1, and then transmit ESD2 and ERR\_ESD3.

# 6.4 Test 3.2.4 - PCS Transmit State Diagram - TRANSMIT DATA state

Purpose: To verify that the DUT properly behaves while in the TRANSMIT DATA state.

### References:

[1] IEEE Std. 802.3bw figure 96-7 – PCS Transmit state diagram

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A test station capable of controlling the MII signals

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

### Discussion:

Reference [1] shows the valid transitions that a 100BASE-T1 device can take through the PCS Transmit State Diagram. Once the DUT enters the TRANSMIT DATA state, it should remain in this state and encode tx\_data until TX\_EN=FALSE.

**Test Setup:** Connect the MII of the Device Under Test (DUT) to the MII test station and the 100BASE-T1 interface of the DUT to the Link Partner via the line tap.

### **Procedure:**

- 1. Configure the test station and Link Partner such that the DUT establishes a valid link while the MII station is sending TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE.

- 2. Instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=FALSE for at least 4 clock cycles.

- 3. Monitor the transmissions from the DUT.

- 4. Repeat steps 1-3, except instruct the MII station to set TXD=0000, TX\_EN=TRUE and TX\_ER=FALSE for at least 4 clock cycles in step 2.

- 5. Repeat steps 1-3, except instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=TRUE for at least 4 clock cycles in step 2.

- Repeat steps 1-3, except instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=FALSE for 4 clock cycles, then set TX\_EN=FALSE and TX\_ER=FALSE for at least 3 clock cycles in step 2.

- 7. Repeat steps 1-3, except instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=TRUE for 4 clock cycles, then set TX\_EN=FALSE and TX\_ER=FALSE for at least 3 clock cycles in step 2.

### Observable Results:

- a. In step 2, the DUT should transmit SSD1, SSD2, and SSD3, then enter the TRANSMIT DATA state and transmit the scrambled version of "010" and "101".

- b. In step 4, the DUT should transmit SSD1, SSD2, and SSD3, then enter the TRANSMIT DATA state and transmit the scrambled version of "000" and "000".

- c. In step 5, the DUT should transmit SSD1, SSD2, and SSD3, then enter the TRANSMIT DATA state and transmit the scrambled version of "010" and "101".

- d. In step 6, the DUT should transmit SSD1, SSD2, and SSD3, then enter the TRANSMIT DATA state and transmit the scrambled version of "010", "101", "0xx", and then transmit ESD1, ESD2, and ESD3. The transmission of "0xx" represents a data bit of 0 and two stuff bits.

e. In step 7, the DUT should transmit SSD1, SSD2, and SSD3, then enter the TRANSMIT DATA state and transmit the scrambled version of "010", "101", "0xx", and then transmit ESD1, ESD2, and ERR\_ESD3. The transmission of "0xx" represents a data bit of 0 and two stuff bits.

# 6.5 Test 3.2.5 - PCS Transmit State Diagram - ESD1 VECTOR state

Purpose: To verify that the DUT properly behaves while in the ESD1 VECTOR state.

### References:

[1] IEEE Std. 802.3bw figure 96-7 – PCS Transmit state diagram

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A test station capable of controlling the MII signals

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

### Discussion:

Reference [1] shows the valid transitions that a 100BASE-T1 device can take through the PCS Transmit State Diagram. Regardless of the transmissions on the MII, once the DUT enters the ESD1 VECTOR state the DUT should transmit ESD1, immediately transition to the ESD2 VECTOR state, and transmit ESD2.

**Test Setup:** Connect the MII of the Device Under Test (DUT) to the MII test station and the 100BASE-T1 interface of the DUT to the Link Partner via the line tap.

### **Procedure:**

- 1. Configure the test station and Link Partner such that the DUT establishes a valid link while the MII station is sending TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE.

- 2. Instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=FALSE for 6 clock cycles, then set TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE for at least 2 clock cycles.

- 3. Monitor the transmissions from the DUT.

- 4. Repeat steps 1-3, except instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=FALSE for 5 clock cycles, then set TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE for 1 clock cycle, and then set TX\_EN=TRUE in step 2.

### **Observable Results:**

- a. In step 2, after exiting the TRANSMIT DATA state, the DUT should transmit ESD1 followed by FSD2.

- b. In step 4, after exiting the TRANSMIT DATA state, the DUT should transmit ESD1 followed by ESD2.

# 6.6 Test 3.2.6 - PCS Transmit State Diagram - ESD2 VECTOR state

**Purpose:** To verify that the DUT properly behaves while in the ESD2 VECTOR state.

### References:

[1] IEEE Std. 802.3bw figure 96-7 – PCS Transmit state diagram

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A test station capable of controlling the MII signals

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

### Discussion:

Reference [1] shows the valid transitions that a 100BASE-T1 device can take through the PCS Transmit State Diagram. Regardless of the transmissions on the MII, once the DUT enters the ESD2 VECTOR state the DUT should transmit ESD2, immediately transition to the ESD3 VECTOR state, and transmit ESD3.

**Test Setup:** Connect the MII of the Device Under Test (DUT) to the MII test station and the 100BASE-T1 interface of the DUT to the Link Partner via the line tap.

### Procedure:

- 1. Configure the test station and Link Partner such that the DUT establishes a valid link while the MII station is sending TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE.

- 2. Instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=FALSE for 5 clock cycles, then set TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE for at least 2 clock cycles.

- 3. Monitor the transmissions from the DUT.

- 4. Repeat steps 1-3, except instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=FALSE for 6 clock cycles, then set TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE for 1 clock cycle, and then set TX\_EN=TRUE in step 2.

### **Observable Results:**

- a. In step 2, after exiting the TRANSMIT DATA state, the DUT should transmit ESD1, ESD2, and ESD3.

- b. In step 4, after exiting the TRANSMIT DATA state, the DUT should transmit ESD1, ESD2, and ESD3.

# 6.7 Test 3.2.7 - PCS Transmit State Diagram - ESD3 VECTOR state

**Purpose:** To verify that the DUT properly behaves while in the ESD3 VECTOR state.

### References:

[1] IEEE Std. 802.3bw figure 96-7 – PCS Transmit state diagram

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A test station capable of controlling the MII signals

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

### Discussion:

Reference [1] shows the valid transitions that a 100BASE-T1 device can take through the PCS Transmit State Diagram. Regardless of the transmissions on the MII, once the DUT enters the ESD3 VECTOR state the DUT should transmit ESD3, immediately transition to the SEND IDLE state, and transmit IDLE.

**Test Setup:** Connect the MII of the Device Under Test (DUT) to the MII test station and the 100BASE-T1 interface of the DUT to the Link Partner via the line tap.

### **Procedure:**

- 1. Configure the test station and Link Partner such that the DUT establishes a valid link while the MII station is sending TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE.

- 2. Instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=FALSE for 8 clock cycles, then set TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE for at least 3 clock cycles.

- 3. Monitor the transmissions from the DUT.

### **Observable Results:**

a. In step 2, after exiting the TRANSMIT DATA state, the DUT should transmit ESD1, ESD2, ESD3, and Idle.

# 6.8 Test 3.2.8 - PCS Transmit State Diagram - ERR ESD1 VECTOR state

**Purpose:** To verify that the DUT properly behaves while in the ESD1 VECTOR state.

### References:

[1] IEEE Std. 802.3bw figure 96-7 – PCS Transmit state diagram

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A test station capable of controlling the MII signals

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

### Discussion:

Reference [1] shows the valid transitions that a 100BASE-T1 device can take through the PCS Transmit State Diagram. Regardless of the transmissions on the MII, once the DUT enters the ERR ESD1 VECTOR state the DUT should transmit ESD1, immediately transition to the ERR ESD2 VECTOR state, and transmit ESD2.

**Test Setup:** Connect the MII of the Device Under Test (DUT) to the MII test station and the 100BASE-T1 interface of the DUT to the Link Partner via the line tap.

### Procedure:

- 1. Configure the test station and Link Partner such that the DUT establishes a valid link while the MII station is sending TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE.

- 2. Instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=TRUE for 6 clock cycles, then set TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE for at least 2 clock cycles.

- 3. Monitor the transmissions from the DUT.

- 4. Repeat steps 1-3, except instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=TRUE for 5 clock cycles, then set TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE for 1 clock cycle, and then set TX\_EN=TRUE in step 2.

### **Observable Results:**

- a. In step 2, after exiting TRANSMIT DATA state, the DUT should transmit ESD1, ESD2, and ERR\_ESD3.

- b. In step 4, after exiting TRANSMIT DATA state, the DUT should transmit ESD1, ESD2, and ERR\_ESD3.

# 6.9 Test 3.2.9 - PCS Transmit State Diagram - ERR ESD2 VECTOR state

Purpose: To verify that the DUT properly behaves while in the ERR ESD2 VECTOR state.

### References:

[1] IEEE Std. 802.3bw figure 96-7 – PCS Transmit state diagram

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A test station capable of controlling the MII signals

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

### Discussion:

Reference [1] shows the valid transitions that a 100BASE-T1 device can take through the PCS Transmit State Diagram. Regardless of the transmissions on the MII, once the DUT enters the ERR ESD2 VECTOR state the DUT should transmit ESD2, immediately transition to the ERR ESD3 VECTOR state, and transmit ERR\_ESD3.

**Test Setup:** Connect the MII of the Device Under Test (DUT) to the MII test station and the 100BASE-T1 interface of the DUT to the Link Partner via the line tap.

### Procedure:

- 1. Configure the test station and Link Partner such that the DUT establishes a valid link while the MII station is sending TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE.

- 2. Instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=TRUE for 5 clock cycles, then set TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE for at least 2 clock cycles.

- 3. Monitor the transmissions from the DUT.

- 4. Repeat steps 1-3, except instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=TRUE for 6 clock cycles, then set TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE for 1 clock cycle, and then set TX\_EN=TRUE in step 2.

### **Observable Results:**

- a. In step 2, after exiting the TRANSMIT DATA state, the DUT should transmit ESD1, ESD2, and ERR ESD3.

- b. In step 4, after exiting the TRANSMIT DATA state, the DUT should transmit ESD1, ESD2, and ERR\_ESD3.

# 6.10 Test 3.2.10 - PCS Transmit State Diagram - ERR ESD3 VECTOR state

Purpose: To verify that the DUT properly behaves while in the ERR ESD3 VECTOR state.

### References:

[1] IEEE Std. 802.3bw figure 96-7 – PCS Transmit state diagram

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A test station capable of controlling the MII signals

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

### Discussion:

Reference [1] shows the valid transitions that a 100BASE-T1 device can take through the PCS Transmit State Diagram. Regardless of the transmissions on the MII, once the DUT enters the ERR ESD3 VECTOR state the DUT should transmit ERR\_ESD3, immediately transition to the SEND IDLE state, and transmit IDLE.

**Test Setup:** Connect the MII of the Device Under Test (DUT) to the MII test station and the 100BASE-T1 interface of the DUT to the Link Partner via the line tap.

### Procedure:

- 1. Configure the test station and Link Partner such that the DUT establishes a valid link while the MII station is sending TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE.

- 2. Instruct the MII station to set TXD=0101, TX\_EN=TRUE, and TX\_ER=TRUE for 8 clock cycles, then set TXD=0000, TX\_EN=FALSE, and TX\_ER=FALSE for at least 3 clock cycles.

- 3. Monitor the transmissions from the DUT.

### **Observable Results:**

a. In step 2, after exiting the TRANSMIT DATA state, the DUT should transmit ESD1, ESD2, ERR\_ESD3, and Idle.

# **GROUP 3: PCS Receive**

# Overview:

The tests defined in this section verify the PCS Receive process defined for 100BASE-T1 capable PHYs in section 96.3.4 of the IEEE 802.3bw 100BASE-T1 Specification.

# 7.1 Test 3.3.1 - Receive PCS Signaling

**Purpose:** To verify that the PCS properly decodes 100BASE-T1 signaling.

### References:

[1] IEEE Std. 802.3bw subclause 96.3.4 – PCS Receive

### **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

### Discussion:

The 100BASE-T1 PCS uses a combination of a 4B3B conversion for MII data, side-stream scrambling, and ternary symbols to encode the data for transmission on the line. In addition to the scrambler, there are additional functions performed on the data and idle eliminate the correlation transmit data and to balance the power density.

This test is designed to ensure that the DUT properly decodes the 100BASE-T1 signaling during training, idle transmission, and data transmission.

**Test Setup:** Connect the Device Under Test (DUT) to the Link Partner via the line tap.

### **Test Procedure:**

- 1. Configure the DUT as MASTER and the Link Partner as SLAVE.

- 2. Connect the DUT to a Link Partner and configure both devices to perform training and establish a link. Monitor the management indications from the DUT.

- 3. Connect the DUT to a Link Partner, establish a link, and configure the Link Partner to transmit valid frames to the DUT. Monitor the management indications from the DUT.

- 4. Connect the DUT to a Link Partner, establish a link, and configure the Link Partner to transmit Idle without frames. Monitor the management indications from the DUT.

- 5. Configure the DUT as SLAVE and the Link Partner as MASTER.

- 6. Connect the DUT to a Link Partner and configure both devices to perform training and establish a link. Monitor the management indications from the DUT.

- 7. Connect the DUT to a Link Partner, establish a link, and configure the Link Partner to transmit valid frames to the DUT. Monitor the management indications from the DUT.

- 8. Connect the DUT to a Link Partner, establish a link, and configure the Link Partner to transmit Idle without frames. Monitor the management indications from the DUT.

### Observable Results:

- a. In step 2 The DUT should accept the idle pattern and establish a link.

- b. In step 3 The DUT should indicate link and should receive valid frames.

- c. In step 4 the DUT should indicate reception of idle and maintain the link.

- d. In step 6 The DUT should accept the idle pattern and establish a link.

- e. In step 7 The DUT should indicate link and should receive valid frames.

- f. In step 8 the DUT should indicate reception of idle and maintain the link.

Possible Problems: None.

# 7.2 Test 3.3.2 - Automatic Polarity Detection (Optional)

**Purpose:** To verify that the PCS properly detects polarity.

#### References:

[1] IEEE Std. 802.3bw subclause 96.3.4.4 – PCS Receive automatic polarity detection (optional)

# **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

# Discussion:

Reference [1] states that the DUT shall automatically detect the polarity of the received signal.

**Test Setup:** Connect the Device Under Test (DUT) to the Link Partner via the line tap.

#### Procedure:

- 1. Connect the DUT to the Link Partner, transmit several frames and observe that the link has successfully been established.

- 2. Switch the polarity by reversing the pair connecting the DUT to the Link Partner. Transmit several frames and observe that the link has successfully been established.

# **Observable Results:**

a. The DUT should establish a link regardless of the receive polarity.

**Possible Problems:** Automatic Polarity Detection is an optional function. This test cannot be completed if the DUT does not implement Automatic Polarity Detection.

# **7.3 Test 3.3.3 - Receive SSD**

**Purpose:** To verify that the PCS properly accepts frames with valid SSD.

# References:

[1] IEEE Std. 802.3bw figure 96-10 – PCS Receive state diagram

[1] IEEE Std. 802.3bw subclause 96.3.4.2 – PCS Receive symbol decoding

# **Resource Requirements:**

- A test station capable of capturing and decoding ternary symbols

- A compliant 100BASE-T1 Link Partner

- A line tap (Refer to appendix 3.C)

# Discussion:

The DUT should accept frames with valid SSD of (0,0), (0,0), (0,0).

**Test Setup:** Connect the Device Under Test (DUT) to the Link Partner via the line tap.

#### **Procedure:**

1. Transmit frames with valid SSD to the DUT while monitoring the DUT transmissions and counters.

# **Observable Results:**

a. The DUT should accept all frames.

# **7.4** Test **3.3.4** - Receive ESD

**Purpose:** To verify that the PCS properly accepts a frame with valid ESD.

# References:

[1] IEEE Std. 802.3bw figure 96-10 – PCS Receive state diagram

[1] IEEE Std. 802.3bw subclause 96.3.4.2 – PCS Receive symbol decoding