# Advanced diagnostic features for 10BASE-T1S automotive Ethernet PHYs Specification

TC14 – advanced PHY features

| Version           | 2.1          |

|-------------------|--------------|

| Date              | May 23, 2025 |

| Status            | Final        |

| Restriction Level | Public       |

|                   |              |

## **VERSION AND RESTRICTION HISTORY OF THIS DOCUMENT**

| VERSION | DESCRIPTION                                                                                                                                                                | RESTRICTION LEVEL              | DATE                                  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------------|

| 0.1     | First Draft Version                                                                                                                                                        | OPEN Technical<br>Members Only | 27 Jan. 2020                          |

|         | 1 <sup>st</sup> - 4 <sup>th</sup> Review of Draft 0.1 (SQI proposals)                                                                                                      | OPEN Technical<br>Members Only | 01 April; 29 April; 13<br>May; 27 May |

|         | 5 <sup>th</sup> Review of Draft 0.1 (PLCA topics)                                                                                                                          | OPEN Technical<br>Members Only | 17 June 2020                          |

|         | 6 <sup>th</sup> Review of Draft 0.1 (PLCA topics)                                                                                                                          | OPEN Technical<br>Members Only | 01 July 2020                          |

|         | 7 <sup>th</sup> Review of Draft 0.1 (SQI; HDD)                                                                                                                             | OPEN Technical<br>Members Only | 15 July 2020                          |

|         | 8 <sup>th</sup> Review of Draft 0.1 (Termination Status; PLCA)                                                                                                             | OPEN Technical<br>Members Only | 22 July 2020                          |

|         | 9 <sup>th</sup> Review of Draft 0.1 (Termination Status; PLCA)                                                                                                             | OPEN Technical<br>Members Only | 26 Aug. 2020                          |

|         | 10 <sup>th</sup> Review of Draft 0.1 (Termination Status; PLCA)                                                                                                            | OPEN Technical<br>Members Only | 23 Sept. 2020                         |

|         | 11 <sup>th</sup> – 14 <sup>th</sup> Review no change                                                                                                                       | OPEN Technical<br>Members Only | 07 Oct.; 21 Oct.; 11<br>Nov.; 25 Nov. |

|         | 15 <sup>th</sup> Review of Draft 0.1 (including PLCA proposal from Tim)                                                                                                    | OPEN Technical<br>Members Only | 14 Jan. 2021                          |

|         | 16 <sup>th</sup> Review of Draft 0.1 (including PLCA proposal from Tim)                                                                                                    | OPEN Technical<br>Members Only | 28 Jan. 2021                          |

|         | 17 <sup>th</sup> Review no change                                                                                                                                          | OPEN Technical<br>Members Only | 18 Febr. 2021                         |

|         | 18 <sup>th</sup> Review of Draft 0.1 (update PLCA)                                                                                                                         | OPEN Technical<br>Members Only | 04 March 2021                         |

|         | 19 <sup>th</sup> Review no change                                                                                                                                          | OPEN Technical<br>Members Only | 18 March 2021                         |

|         | 20 <sup>th</sup> Review of Draft 0.1 (update SQI; add SQITOID)                                                                                                             | OPEN Technical<br>Members Only | 08 April 2021                         |

|         | 21 <sup>st</sup> no change                                                                                                                                                 | OPEN Technical<br>Members Only | 22 April 2021                         |

|         | 22 <sup>nd</sup> update of SQI and SQITOID                                                                                                                                 | OPEN Technical<br>Members Only | 06 May 2021                           |

| 0.2     | 23 <sup>rd</sup> update of SQI (3 level); remove BET until further evaluation results are available; update abbreviation; preparing for final review at sub working group. | OPEN Technical<br>Members Only | 20 May 2021                           |

| 0.3  | 24 <sup>th</sup> update. Include feedback of the sub<br>working group members. Version to be<br>forwarded to the OPEN Steering Committee<br>for review.                                                                                | OPEN Technical<br>Members Only | 10 June 2021                    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------|

| 0.31 | 1 <sup>st</sup> intermediate stage with evaluated TC14 review results                                                                                                                                                                  | OPEN Technical<br>Members Only | 08 July 2021                    |

| 0.32 | 2 <sup>nd</sup> intermediate stage with evaluated TC14 review results                                                                                                                                                                  | OPEN Technical<br>Members Only | 22 July 2021                    |

| 1.0  | Final version                                                                                                                                                                                                                          | OPEN Technical<br>Members Only | 28 Oct. 2021                    |

| 1.1  | Updated copyright and disclaimer.<br>Changed Restriction Level to Public<br>Finalized                                                                                                                                                  | Public                         | 15 Feb. 2022                    |

| 1.2  | Reopening of subworking group for specification update discussion (Received feedback see Point 1 – 3 (5.1.1; 5.1.2; 5.2.1) in this document and separate NXP presentation "10BASE-T1S Advanced Diagnostics 2022-12-02 Matthias Muth".) |                                | 09 Jan. 2023                    |

| 1.3  | Complete document (Draft)                                                                                                                                                                                                              |                                | 03 Feb. 2023                    |

| 1.4  | 5.2.1; 5.2.2                                                                                                                                                                                                                           |                                | 21 Feb. 2023                    |

| 1.5  | 2; 3; 4; 5.2.1; 5.2.2                                                                                                                                                                                                                  |                                | 23 May 2023                     |

| 1.6  | 4; 5                                                                                                                                                                                                                                   |                                | 27 June 2023                    |

| 1.7  | 4;5                                                                                                                                                                                                                                    |                                | 14 July 2023                    |

| 1.8  | 4; 5.2.2                                                                                                                                                                                                                               |                                | 14 Sept. 2023                   |

| 1.9  | 4; 5.2.2                                                                                                                                                                                                                               |                                | 20 Sept. 2023                   |

| 1.10 | 4 (Table 1); 5.1.1 (Table 6); 5.2                                                                                                                                                                                                      |                                | 23 Oct. 2023                    |

| 1.11 | 4 (Table 1); 5.1.1                                                                                                                                                                                                                     |                                | 05 Feb. 2024                    |

| 1.12 | 4 (Table 1); 5.1.1                                                                                                                                                                                                                     |                                | 09 Feb. 2024                    |

| 1.13 | 5.1.1; 5.2; 5.3; including comments from Piergiorgio                                                                                                                                                                                   |                                | 20 March 2024                   |

| 1.14 | 4 (Table 1); 5.1; 5.2; 5.3; PLCAD removed                                                                                                                                                                                              |                                | 17 May 2024                     |

| 1.15 | 4 (Table 1); 5.2; 5.2.2.5; 5.2.2.6; HDD-<br>Ready Table 8. 1. Review                                                                                                                                                                   |                                | 4/7 June 2024<br>3/12 July 2024 |

| 1.16 | 2. Review; Abbreviation; Remark 1) at Table 1; Table 8; 5.3.3.2 SQI+                                                                                                                                                                   |                                | 26 July 2024                    |

| 1.17 | 4 Table 1; 5.2.2 Table 8                                                                                                                                                                                                               |                                | 20 Sept. 2024                   |

| 1.18 | 4 Table 1; 5.2.2 Table 8; 5.2.2.3 Table 11                                                                                                                                                                                             |                                | 07 Oct. 2024                    |

|      |                                                                                                                                                                                                                                        |                                |                                 |

| 1.19 | 4 Table 1                                                                                                                                                |                                | 21 Oct. 2024 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------|

| 1.20 | 4 Table 1; Default values of different register parameters                                                                                               |                                | 15 Nov. 2024 |

| 1.21 | Update Note at node term definition.<br>Add note at 4.1 Table 2; 4.1.1 Table 3; 4.2.2<br>Table 8; 4.2.2.1 Table 10; 4.2.2.2 Table 11;<br>4.2.2.4 Table13 |                                | 26 Nov. 2024 |

| 2.0  | Normative references; Node term definition; 4.2.1                                                                                                        | OPEN Technical<br>Members Only | 06 Dec. 2024 |

| 2.1  | Adjustment to the new OPEN Alliance specification template                                                                                               | Public                         | 23.May. 2025 |

## **CHAIR AND VICE CHAIR**

| CHAIR                         | NAME               | ORGANIZATION          |

|-------------------------------|--------------------|-----------------------|

| OPEN Alliance TC14 Chair      | Samuel Sigfridsson | Volvo Car Corporation |

| OPEN Alliance TC14 Vice Chair | Patrick Isensee    | C&S group GmbH        |

## **EDITOR**

| NAME           | ORGANIZATION |

|----------------|--------------|

| Thomas Lindner | BMW AG       |

## **CONTRIBUTORS**

| NAME               | ORGANIZATION      |

|--------------------|-------------------|

| Tim Baggett        | Microchip         |

| Piergiorgio Beruto | Onsemi            |

| Mingzhang Bian     | Daimler Truck     |

| David Bollati      | C&S group GmbH    |

| Filip Brtan        | Onsemi            |

| Clemens de Haas    | NXP               |

| Venkat lyer        | Microchip         |

| Thomas Lindner     | BMW AG (editor)   |

| Wei Lou            | Broadcom          |

| Matthias Muth      | NXP               |

| Guillermo Oliver   | Analog Devices    |

| Antonio Orzelli    | Canova Tech s.r.l |

| Jibu Palathanam    | Ford              |

| Viliam Vozar       | Onsemi            |

# **Table of Contents**

| V | VERSION AND RESTRICTION HISTORY OF THIS DOCUMENT                                                | 2    |

|---|-------------------------------------------------------------------------------------------------|------|

| С | CHAIR AND VICE CHAIR                                                                            | 5    |

| E | EDITOR                                                                                          | 5    |

| С | CONTRIBUTORS                                                                                    | 5    |

| 1 | 1 OPEN SPECIFICATION OWNERSHIP AND USAGE RIGHTS                                                 | 8    |

| 2 | 2 RIGHTS AND USAGE RESTRICTIONS SPECIFIC TO OPEN ALLIANCE MEMBERS.                              | 8    |

|   | 2.1 Rights and Usage Restrictions Specific to Non-members of OPEN Alliance                      | 8    |

| 3 | 3 TERMS APPLICABLE TO BOTH MEMBERS AND NON-MEMBERS OF OPEN ALLIA                                | NCE9 |

|   | 3.1 Patents, Trademarks, and other Rights:                                                      | 9    |

|   | 3.2 Disclaimers and Limitations of Liability:                                                   | 9    |

|   | 3.3 Compliance with Laws and Regulations:                                                       | 9    |

|   | 3.4 Automotive Applications Only:                                                               | 10   |

|   | 3.5 Right to Withdraw or Modify:                                                                | 10   |

| 4 | 4 INTRODUCTION                                                                                  | 11   |

| 5 | 5 ABBREVIATION/SYMBOLS                                                                          | 11   |

| 6 | 6 SCOPE                                                                                         | 12   |

| 7 | 7 NORMATIVE REFERENCES                                                                          | 12   |

| 8 | 8 TERMS AND DEFINITIONS                                                                         | 12   |

| 9 | 9 OVERVIEW                                                                                      | 13   |

|   | 9.1 Advanced Diagnostic features capability (ADFCAP)                                            | 14   |

|   | 9.1.1 HDD class capability                                                                      |      |

|   | 9.1.2 SQI+ class capability                                                                     |      |

|   | 9.1.3 SQI class capability                                                                      | 16   |

|   | 9.2 Harness Defect Detection (HDD)                                                              |      |

|   | 9.2.1 HDD classes with their resistive thresholds                                               |      |

|   | 9.2.2 HDD (HDD_CTRL; HDD_READY; START_CTRL; VALID; SHORT_OPEN_ST) register 9.2.3 HDD_CTRL field |      |

|   | 9.2.4 HDD_READY field                                                                           |      |

|   | 9.2.5 START_CTRL field                                                                          |      |

| 9.2.6 | VALID                                           |    |

|-------|-------------------------------------------------|----|

| 9.2.7 | SHORT_OPEN_ST                                   | 22 |

|       | ynamic Channel Quality                          |    |

| -     | SQI Transmit Opportunity ID (DCQ.TOID) register |    |

| 9.3.2 | SQI (DCQ.SQI.UPDATE; DCQ.SQI) register          | 24 |

| 9.3.3 | DCO.SOI+ (DCO.SOI+.UPDATE: DCO.SOI+) register   | 30 |

OPEN Alliance Specification Copyright Notice and Disclaimer

#### 1 OPEN SPECIFICATION OWNERSHIP AND USAGE RIGHTS

As between OPEN Alliance and OPEN Alliance Members whose contributions were incorporated in this OPEN Specification (the "Contributing Members"), the Contributing Members own the worldwide copyrights in and to their given contributions. Other than the Contributing Members' contributions, OPEN Alliance owns the worldwide copyrights in and to compilation of those contributions forming this OPEN Specification. For OPEN Alliance Members (as that term is defined in the OPEN Alliance Bylaws), OPEN Alliance permits the use of this OPEN Specification on the terms in the OPEN Alliance Intellectual Property Rights Policy and the additional applicable terms below. For non-members of OPEN Alliance, OPEN Alliance permits the use of this OPEN Specification on the terms in the OPEN Alliance Specification License Agreement (available here: <a href="https://www.opensig.org/Automotive-Ethernet-Specifications/">https://www.opensig.org/Automotive-Ethernet-Specifications/</a>) and the additional applicable terms below. The usage permissions referenced and described here relate only to this OPEN Specification and do not include or cover a right to use any specification published elsewhere and referred to in this OPEN Specification. By using this OPEN Specification, you hereby agree to the following terms and usage restrictions:

## 2 RIGHTS AND USAGE RESTRICTIONS SPECIFIC TO OPEN ALLIANCE MEMBERS

FOR OPEN ALLIANCE MEMBERS ONLY: In addition to the usage terms and restrictions granted to Members in the OPEN Alliance Intellectual Property Rights Policy, Members' use of this OPEN Specification is subject this Copyright Notice and Disclaimer. Members of OPEN Alliance have the right to use this OPEN Specification solely (i) during the term of a Member's membership in OPEN Alliance and subject to the Member's continued membership in good standing in OPEN Alliance; (ii) subject to the Member's continued compliance with the OPEN Alliance governance documents, Intellectual Property Rights Policy, and the applicable OPEN Alliance Promoter or Adopter Agreement, as applicable; and (iii) for internal business purposes and solely to use the OPEN Specification for implementation of this OPEN Specification in the Member's products and services, but only so long as Member does not distribute, publish, display, or transfer this OPEN Specification to any third party, except as expressly set forth in Section 11 of the OPEN Alliance Intellectual Property Rights Policy. Except and only to the extent required to use this OPEN Specification internally for implementation of this OPEN Specification in Member's products and services, Member shall not modify, alter, combine, delete portions of, prepare derivative works of, or create derivative works based upon this OPEN Specification. If Member creates any modifications, alterations, or other derivative works of this OPEN Specification as permitted to use the same internally for implementation of this OPEN Specification in Member's products and services, all such modifications, alterations, or other derivative works shall be deemed part of, and licensed to such Member under the same restrictions as, this OPEN Specification. For the avoidance of doubt, Member shall not include all or any portion of this OPEN Specification in any other technical specification or technical material, product manual, marketing material, or any other material without OPEN Alliance's prior written consent. All rights not expressly granted to Member in the OPEN Alliance Intellectual Property Rights Policy are reserved;

## 2.1 Rights and Usage Restrictions Specific to Non-members of OPEN Alliance

FOR NON-MEMBERS OF OPEN ALLIANCE ONLY: Use of this OPEN Specification by anyone who is not a Member in good standing of OPEN Alliance is subject to your agreement to the OPEN Alliance Specification License Agreement (available here: <a href="http://www.opensig.org/Automotive-Ethernet-Specifications/">http://www.opensig.org/Automotive-Ethernet-Specifications/</a>) and the additional terms in this Copyright Notice and Disclaimer. Non-members have the right to use this OPEN Specification solely (i) subject to the non-member's continued compliance with the OPEN Alliance Specification License Agreement; and (ii) for internal business purposes and solely to use the OPEN Specification for implementation of this OPEN Specification in the non-member's products and services, but only so long as non-member does not distribute, publish, display, or transfer this OPEN Specification to any third party, unless and only to the extent expressly set forth in the OPEN Alliance Specification License

Agreement. Except and only to the extent required to use this OPEN Specification internally for implementation of this OPEN Specification in non-member's products and services, non-member shall not modify, alter, combine, delete portions of, prepare derivative works of, or create derivative works based upon this OPEN Specification. If non-member creates any modifications, alterations, or other derivative works of this OPEN Specification as permitted to use the same internally for implementation of this OPEN Specification in non-member's products and services, all such modifications, alterations, or other derivative works shall be deemed part of, and licensed to such non-member under the same restrictions as, this OPEN Specification. For the avoidance of doubt, non-member shall not include all or any portion of this OPEN Specification in any other technical specification or technical material, product manual, marketing material, or any other material without OPEN Alliance's prior written consent. All rights not expressly granted to non-member in the OPEN Alliance Specification License Agreement are reserved.

## 3 TERMS APPLICABLE TO BOTH MEMBERS AND NON-MEMBERS OF OPEN ALLIANCE

#### 3.1 Patents, Trademarks, and other Rights:

OPEN Alliance has received no Patent Disclosure and Licensing Statements related to this OPEN Specification. Therefore, this OPEN Specification contains no specific disclaimer related to third parties that may require a patent license for their Essential Claims. Having said that, the receipt of this OPEN Specification shall not operate as an assignment of or license under any patent, industrial design, trademark, or other rights as may subsist in or be contained in or reproduced in this OPEN Specification; and the implementation of this OPEN Specification could require such a patent license from a third party. You may not use any OPEN Alliance trademarks or logos without OPEN Alliance's prior written consent.

## 3.2 Disclaimers and Limitations of Liability:

THIS OPEN SPECIFICATION IS PROVIDED ON AN "AS IS" BASIS, AND ALL REPRESENTATIONS, WARRANTIES, AND GUARANTEES, EITHER EXPLICIT, IMPLIED, STATUTORY, OR OTHERWISE, ARE EXCLUDED AND DISCLAIMED UNLESS (AND THEN ONLY TO THE EXTENT THEY ARE) MANDATORY UNDER LAW. ACCORDINGLY, OPEN ALLIANCE AND THE CONTRIBUTING MEMBERS MAKE NO REPRESENTATIONS OR WARRANTIES OR GUARANTEES WITH REGARD TO THIS OPEN SPECIFICATION OR THE INFORMATION (INCLUDING ANY SOFTWARE) CONTAINED HEREIN. OPEN ALLIANCE AND ALL CONTRIBUTING MEMBERS HEREBY EXPRESSLY DISCLAIM ANY AND ALL SUCH EXPRESS, IMPLIED, STATUTORY, AND ALL OTHER REPRESENTATIONS, WARRANTIES, AND GUARANTEES, INCLUDING WITHOUT LIMITATION ANY AND ALL WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR USE, TITLE, NON-INFRINGEMENT OF OR ABSENCE OF THIRD PARTY RIGHTS, AND/OR VALIDITY OF RIGHTS IN THIS OPEN SPECIFICATION; AND OPEN ALLIANCE AND THE CONTRIBUTING MEMBERS MAKE NO REPRESENTATIONS AS TO THE ACCURACY OR COMPLETENESS OF THIS OPEN SPECIFICATION OR ANY INFORMATION CONTAINED HEREIN. WITHOUT LIMITING THE FOREGOING, OPEN ALLIANCE AND/OR CONTRIBUTING MEMBERS HAS(VE) NO OBLIGATION WHATSOEVER TO INDEMNIFY OR DEFEND YOU AGAINST CLAIMS RELATED TO INFRINGEMENT OR MISAPPROPRIATION OF INTELLECTUAL PROPERTY RIGHTS. OPEN ALLIANCE AND CONTRIBUTING MEMBERS ARE NOT, AND SHALL NOT BE, LIABLE FOR ANY LOSSES, COSTS, EXPENSES, OR DAMAGES OF ANY KIND WHATSOEVER (INCLUDING WITHOUT LIMITATION DIRECT, INDIRECT, SPECIAL, INCIDENTAL, CONSEQUENTIAL, PUNITIVE, AND/OR EXEMPLARY DAMAGES) ARISING IN ANY WAY OUT OF USE OR RELIANCE UPON THIS OPEN SPECIFICATION OR ANY INFORMATION HEREIN. NOTHING IN THIS DOCUMENT OPERATES TO LIMIT OR EXCLUDE ANY LIABILITY FOR FRAUD OR ANY OTHER LIABILITY WHICH IS NOT PERMITTED TO BE EXCLUDED OR LIMITED BY OPERATION OF LAW.

## 3.3 Compliance with Laws and Regulations:

NOTHING IN THIS DOCUMENT OBLIGATES OPEN ALLIANCE OR CONTRIBUTING MEMBERS TO PROVIDE YOU WITH SUPPORT FOR, OR RELATED TO, THIS OPEN SPECIFICATION OR ANY IMPLEMENTED PRODUCTS OR SERVICES. NOTHING IN THIS OPEN SPECIFICATION CREATES ANY WARRANTIES OR GUARANTEES, EITHER EXPRESS OR IMPLIED, STATUTORY OR OTHERWISE, REGARDING ANY LAW OR REGULATION. OPEN ALLIANCE AND CONTRIBUTING MEMBERS EXPRESSLY DISCLAIM ALL LIABILITY, INCLUDING WITHOUT LIMITATION, LIABILITY FOR NONCOMPLIANCE WITH LAWS, RELATING TO

USE OF THE OPEN SPECIFICATION OR INFORMATION CONTAINED HEREIN. YOU ARE SOLELY RESPONSIBLE FOR THE COMPLIANCE OF IMPLEMENTED PRODUCTS AND SERVICES WITH ANY SUCH LAWS AND REGULATIONS, AND FOR OBTAINING ANY AND ALL REQUIRED AUTHORIZATIONS, PERMITS, AND/OR LICENSES FOR IMPLEMENTED PRODUCTS AND SERVICES RELATED TO SUCH LAWS AND REGULATIONS WITHIN THE APPLICABLE JURISDICTIONS.

IF YOU INTEND TO USE THIS OPEN SPECIFICATION, YOU SHOULD CONSULT ALL APPLICABLE LAWS AND REGULATIONS. COMPLIANCE WITH THE PROVISIONS OF THIS OPEN SPECIFICATION DOES NOT CONSTITUTE COMPLIANCE TO ANY APPLICABLE LEGAL OR REGULATORY REQUIREMENTS. IMPLEMENTERS OF THIS OPEN SPECIFICATION ARE SOLELY RESPONSIBLE FOR OBSERVING AND COMPLYING WITH THE APPLICABLE LEGAL AND REGULATORY REQUIREMENTS. WITHOUT LIMITING THE FOREGOING, YOU SHALL NOT USE, RELEASE, TRANSFER, IMPORT, EXPORT, AND/OR RE-EXPORT THIS OPEN SPECIFICATION OR ANY INFORMATION CONTAINED HEREIN IN ANY MANNER PROHIBITED UNDER ANY APPLICABLE LAWS AND/OR REGULATIONS, INCLUDING WITHOUT LIMITATION U.S. EXPORT CONTROL LAWS.

## 3.4 Automotive Applications Only:

Without limiting the foregoing disclaimers or limitations of liability in any way, this OPEN Specification was developed for automotive applications only. This OPEN Specification has neither been developed, nor tested for, non-automotive applications.

#### 3.5 Right to Withdraw or Modify:

OPEN Alliance reserves the right to (but is not obligated to) withdraw, modify, or replace this OPEN Specification at any time, without notice.

© 2024 OPEN Alliance. This document also contains contents, the copyrights of which are owned by third parties who are OPEN Alliance Contributing Members. Unauthorized Use Strictly Prohibited. All Rights Reserved.

## 4 INTRODUCTION

This specification describes advanced features of a 10BASE-T1S automotive Ethernet PHY (often also called transceiver), e.g. for diagnostic purposes for automotive Ethernet Phis

## 5 ABBREVIATION/SYMBOLS

| AWG noise | Added White Gaussian noise                                                                    |

|-----------|-----------------------------------------------------------------------------------------------|

| BER       | Bit Error Rate                                                                                |

| CRC       | Cyclic Redundancy Check                                                                       |

| DCQ       | Dynamic Channel Quality                                                                       |

| DigPHY    | PHY without analog PMA portion which is left into a separate chip (i.e., the PMD transceiver) |

| ED        | Energy Detect                                                                                 |

| HDD       | Harness defect detection                                                                      |

| MDI       | Medium Dependent Interface                                                                    |

| OSD       | OPEN/SHORT detection                                                                          |

| PHY       | PHY is a Physical layer interface device, often called transceiver                            |

| SNR       | Signal Noise Ratio                                                                            |

| SQI       | Signal Quality Index (8 levels)                                                               |

| SQI+      | Signal Quality Index (8 up to 256 levels)                                                     |

| TOID      | Transmit Opportunity ID                                                                       |

|           |                                                                                               |

#### 6 SCOPE

The objective of this document is to provide a standard set of Advanced PHY features for 10BASE-T1S implementations.

## 7 NORMATIVE REFERENCES

The following documents are referred to in the text in such a way that some or all of their content constitutes requirements of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

[1] IEEE Std 802.3<sup>™</sup> - 2022, IEEE Standard for Ethernet

[2] OPEN Alliance: 10BASE-T1S PMD Transceiver Interface

[3] OPEN Alliance: 10BASE-T1S Physical Media Attachment Test Suite

[4] OPEN Alliance: 10BASE-T1S Half-Duplex Interoperability Test Suite

[5] OPEN Alliance: 10BASE-T1S System implementation specification

## **8 TERMS AND DEFINITIONS**

For the purposes of this document, the following terms and definitions apply.

ISO and IEC maintain terminological databases for use in standardization at the following addresses:

- ISO Online browsing platform: available at <a href="https://www.iso.org/obp">https://www.iso.org/obp</a>

- IEC Electropedia: available at <a href="http://www.electropedia.org/">http://www.electropedia.org/</a>

## Node term definition:

|             | A node that is at either end of a mixing segment. There are no other nodes between the End                                                                                                  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| End Node    | Node and the 100 $\!\Omega$ edge termination. The End Node may contain the 100 $\!\Omega$ edge termination.                                                                                 |

| Drop Node   | Any node that is located between the two end nodes                                                                                                                                          |

| Coordinator | This is the node configured as aPLCALocalNodeID=0 that is responsible for the periodic transmission of the BEACON and configuring the number of transmit opportunities between each BEACON. |

| Follower    | Followers are any nodes configured as aPLCALocalNodeID=1254. They synchronize their transmit opportunity counter with the reception of the periodic BEACON transmitted by the coordinator   |

| Head Node   | This is the highest-level application node on the mixing segment. It typically implements a switch or gateway access to the core network beyond the bus segment.                            |

#### Note:

It is expected that each segment includes two end nodes, one coordinator and one head node.

## 9 **OVERVIEW**

10BASE-T1S automotive Ethernet transceivers (PHY or every PHY port of a switch) shall offer the information specified below for diagnostic purposes.

| group  | group<br>name                                  | parameter         | parameter<br>name                      | Description                                                                                                                                 | remarks |

|--------|------------------------------------------------|-------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------|

| ADFCAP | Advanced diagnostic features capability        | HDD               | HDD capability                         | Indication of HDD capability and of supported HDD class (HDDx; x= 1;2)                                                                      | 3)      |

|        |                                                | SQI+              | SQI+ capability                        | Indication of SQI+ capability and of used bits for the SQI+ value.                                                                          |         |

|        |                                                | SQI               | SQI capability                         | Indication of SQI capability.                                                                                                               |         |

| HDD    | Harness<br>defect<br>detection                 | HDD_CTRL          | HDD control                            | Ctrl. Bit for enabling request of HDD function.                                                                                             | 2) 3)   |

|        |                                                | HDD_READY         | HDD Ready                              | Status feedback                                                                                                                             | 2) 3)   |

|        |                                                | START_CTRL        | Start<br>measurement                   | Ctrl. Bit for starting Measurement and indication bit for Measurement in progress.                                                          | 2) 3)   |

|        |                                                | VALID             | Measurement results ready and valid    | Indication bit for measurement results ready and valid.                                                                                     | 2) 3)   |

|        |                                                | SHORT_<br>OPEN_ST | Bus short/open status                  | Indication bit for bus short/open condition detected                                                                                        | 2) 3)   |

| DCQ    | Dynamic channel quality is applicable for PHY. | TOID              | SQI/SQI+<br>Transmit<br>Opportunity ID | The SQI/SQI+ value is determined for only a specific transmitting node as identified by the PLCA transmit opportunity as configured in TOID |         |

|        |                                                | SQI.UPDATE        | SQI Update<br>Indication               | SQI was updated since last read.                                                                                                            |         |

|        |                                                | SQI               | Signal Quality<br>Index                | Current SQI value. A classification of the signal quality with 8 levels                                                                     | 1)      |

|        |                                                | SQI+.UPDATE       | SQI+ Update<br>Indication              | SQI was updated since last read.                                                                                                            |         |

|        |                                                | SQI+              | Signal Quality<br>Index Plus           | Current SQI+ value. A classification of the signal quality with 8 up to 256 levels.                                                         |         |

Table 1: Overview of required PHY parameters to be stored and provided via Register fields

## Remarks to Table 1:

- 1) "The SQI levels, at least 8 (3 bits), have a recommended correlation to BER as shown in Table 19 and for jitter  $\leq$  15ns @MDI (see [5]) the SQI value shall be  $\geq$  3."

- 2) Diagnostic function is only available in special "diagnostic" mode, not on the fly.

- 3) For PMD Transceiver, HDD function may be located in PMD Transceiver. In this case, the HDD capability and control registers should be at location x04 and x05 of PMD Transceiver. If HDD function is located in digPHY, the HDD capability and control registers are at location xCC00 and xCC01.

## 9.1 Advanced Diagnostic features capability (ADFCAP)

Before defining the different diagnostic features like HDD (Harness defect detection) and SQI (Signal Quality Index), it makes sense to define the capability a PHY can support and where this information is available."

For supporting most of system implementation requirements, HDD and SQI diagnostic features were split into diagnostic subclasses.

In this document four diagnostic classes for HDD are defined: HDD1, HDD2, HDD3, HDD4; and two diagnostic classes for SQI are defined: SQI and SQI+."

Due to various diagnostic functions and their subclasses, in Table 2 the capability register is shown in which the PHY information of supported diagnostic classes are accessible.

| Register Name | ADFCAP                                  |

|---------------|-----------------------------------------|

| Description   | Advanced diagnostic features capability |

| size[bits]    | 16                                      |

| MMD           | 31                                      |

| Addr/Offset   | 0xCC00/0 *                              |

<sup>\*</sup>In case PMD Transceiver is used for diagnostics in this specification the capability register shall be at location x04 of PMD Transceiver.

| 15       | 14 | 13 | 12 | 11 | 10  | 9   | 8   |  |  |  |

|----------|----|----|----|----|-----|-----|-----|--|--|--|

| Reserved |    |    |    |    | HDD |     |     |  |  |  |

|          | RO |    |    |    |     | RO  |     |  |  |  |

| 7        | 6  | 5  | 4  | 3  | 2   | 2 1 |     |  |  |  |

| Reserved |    |    |    | sq | l+  |     | SQI |  |  |  |

| RO       |    |    |    | R  | )   |     | RO  |  |  |  |

| Bit(s) | Name     | Description            | Access |  |  |

|--------|----------|------------------------|--------|--|--|

| 15:11  | Reserved | Reserved (Default = 0) | RO     |  |  |

| 10:8 | HDD      | Harness Defect Detection capability 0 – HDD is not supported X – HDD class X is supported | RO |

|------|----------|-------------------------------------------------------------------------------------------|----|

| 7:5  | Reserved | Reserved (Default = 0)                                                                    | RO |

| 4:1  | SQI+     | SQI+ capability 0 – SQI+ is not supported X – SQI+ is supported using X bits              | RO |

| 0    | SQI      | SQI capability 0 – SQI is not supported 1 – SQI is supported                              | RO |

Table 2: Definition of ADFCAP register

## 9.1.1 HDD class capability

Harness Defect Detection capability information for supported HDD class.

| Field Name  | ADFCAP.HDD                          |

|-------------|-------------------------------------|

| Description | Harness Defect Detection capability |

| size[bits]  | 3                                   |

| MMD         | 31                                  |

| Addr/Offset | 0xCC00 / 8 *                        |

<sup>\*</sup>In case PMD Transceiver is used for diagnostics in this specification the capability register shall be at location x04 of PMD Transceiver.

| Field value | Explanation (ADFCAP.HDD)            |

|-------------|-------------------------------------|

| 0x0         | 0 - HDD is not supported            |

| 0x1         | 1 – HDD1 (HDD class 1 is supported) |

| 0x2         | 2 – HDD2 (HDD class 2 is supported) |

| 0x3         | 3 – HDD3 (HDD class 3 is supported) |

| 0x4         | 4 – HDD4 (HDD class 4 is supported) |

| 0x5         | Reserved                            |

| 0x6         | Reserved                            |

| 0x7         | Reserved                            |

Table 3: Definition of HDD field in the ADFCAP register

# 9.1.2 SQI+ class capability

SQI+ capability information for supported SQI+ class and used numbers of bits.

| Field Name  | ADFCAP.SQI+     |

|-------------|-----------------|

| Description | SQI+ capability |

| size[bits]  | 4               |

| MMD         | 31              |

| Addr/Offset | 0xCC00 / 1      |

| Field value | Explanation (ADFCAP.SQI+)                        |

|-------------|--------------------------------------------------|

| 0x0         | 0 – SQI+ is not supported                        |

| 0x1         | Reserved                                         |

| 0x2         | Reserved                                         |

| 0x3         | 3 – SQI+ is supported, using 3 bits (8 levels)   |

| 0x4         | 4 – SQI+ is supported, using 4 bits (16 levels)  |

| 0x5         | 5 – SQI+ is supported, using 5 bits (32 levels)  |

| 0x6         | 6 – SQI+ is supported, using 6 bits (64 levels)  |

| 0x7         | 7 – SQI+ is supported, using 7 bits (128 levels) |

| 0x8         | 8 – SQI+ is supported, using 8 bits (256 levels) |

| 0x9         | Reserved                                         |

| 0xA         | Reserved                                         |

| 0xB         | Reserved                                         |

| 0xC         | Reserved                                         |

| 0xD         | Reserved                                         |

| 0xE         | Reserved                                         |

| 0xF         | Reserved                                         |

Table 4: Definition of SQI+ field in the ADFCAP register

## 9.1.3 SQI class capability

SQI+ capability information for supported SQI class of the used PHY

| Field Name  | ADFCAP.SQI     |

|-------------|----------------|

| Description | SQI capability |

| size[bits]  | 1              |

| MMD         | 31             |

| Addr/Offset | 0xCC00 / 0 |

|-------------|------------|

|-------------|------------|

| Field value | Explanation (ADFCAP.SQI)                      |

|-------------|-----------------------------------------------|

| 0x0         | 0 – SQI is not supported                      |

| 0x1         | 1 – SQI is supported, using 3 bits (8 levels) |

Table 5: Definition of SQI field in the ADFCAP register

## 9.2 Harness Defect Detection (HDD)

There shall be a possibility to detect harness defects. This can either be done during normal operation (as long as possible) or in a specific host-triggered diagnostic mode.

This procedure should be controlled via defined registers. Before the procedure is started, all other nodes connected to the same line should be prevented from any transmission.

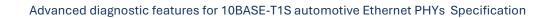

Figure 1 shows an overview of all possible short circuits and open wire states including differential end termination mismatch. The physical positions are to be understood as examples. Based on this image, the following Table 6 shows which errors can be generated:

Figure 1: Overview of possible harness defects.

Table 6 is showing the Bus Failure Matrix, indicating which combinations of failures and environmental conditions belongs to which HDD diagnostic.

|                                      | Roc_P | RocN        | RSC_BAT_P | RSC_BAT_N | RSC_GND_P | RSC_GND_N | RSC_P_N | R <sub>T_1</sub> | $R_{T_2}$ |

|--------------------------------------|-------|-------------|-----------|-----------|-----------|-----------|---------|------------------|-----------|

| Fault 1: Single Wire Open P          | R     | 0<br>R      |           |           |           |           |         | 100              | 100       |

| Fault 2: Single Wire Open N          | 0     |             |           |           |           |           |         | 100              | 100       |

| Fault 3: Double Wire Open            | R     | R           |           |           |           |           |         | 100              | 100       |

| Fault 4: Single Wire Short BAT P     | 0     | 0           | R         | 11.22     |           |           |         | 100              | 100       |

| Fault 5: Single Wire Short BAT N     | 0     |             |           | R         | 0.515     |           |         | 100              | 100       |

| Fault 6: Single Wire Short GND P     | 0     | 0           |           |           | R         |           |         | 100              | 100       |

| Fault 7: Single Wire Short GND N     | 0     | 0           |           |           |           | R         | -       | 100              | 100       |

| Fault 8: Short P to N                | 0     | 0           |           |           |           |           | R       | 100              | 100       |

| Fault 9: Double Wire Short to BAT    |       | 0           | R         |           |           |           | 0       | 100              | 100       |

| Fault 10: Double Wire Short to GND   | 0     | 0           |           |           | R         |           | 0       | 100              | 100       |

| Fault 11: Single Termination Missing | 0     | 0           |           |           |           |           |         | 100              |           |

| Fault 12: Double Termination Missing | 0     | 0 0 0 0 0 0 |           |           |           |           |         |                  | 100       |

Table 6: Bus Failure Matrix

## 9.2.1 HDD classes with their resistive thresholds

The supported failure cases of each HDD class with its resistive thresholds are given in Table 7.

The defined resistive thresholds are relating only to the physical channel, consisting of PCB plugs, contacts, wire, and inline connectors.

From a PHY perspective, the impact of series coupling capacitors and of further components for example CMC, ESD, 1.5 k $\Omega$  CMT (common mode termination) have to be considered at the PHY HDD implementation in addition to that given resistive threshold limits.

|                                                   | HDD Class 1 Open / Short HDD Class 2 SW Open / Short |                          | HDD C                    |                          | 1000000                         | Class 4<br>/ sw short    |                                 |                            |

|---------------------------------------------------|------------------------------------------------------|--------------------------|--------------------------|--------------------------|---------------------------------|--------------------------|---------------------------------|----------------------------|

| Failure Case                                      | HARD                                                 |                          |                          |                          | WE                              | AK                       |                                 |                            |

| Reporting:                                        | ок                                                   | FAIL                     | ок                       | FAIL                     | ок                              | FAIL                     | ок                              | FAIL                       |

| Open of both wires                                | R <sub>oc</sub> ≤ 2.5 Ω                              | R <sub>oc</sub> ≥ 100 kΩ | R <sub>oc</sub> ≤ 2.5 Ω  | R <sub>oc</sub> ≥ 100 kΩ | R <sub>oc</sub> ≤ 20 Ω          | R <sub>oc</sub> ≥ 100 Ω  | R <sub>oc</sub> ≤ 20 Ω          | R <sub>oc</sub> ≥ 100 Ω    |

| Short of both wires to<br>GND or VBAT             | $R_{\text{SC}} \geq 100 \; k\Omega$                  | R <sub>sc</sub> ≤ 10 Ω * | R <sub>sc</sub> ≥ 100 kΩ | R <sub>sc</sub> ≤ 10 Ω * | $R_{SC} \ge 10 \text{ k}\Omega$ | $R_{sc} \le 1 k\Omega *$ | $R_{SC} \ge 10 \text{ k}\Omega$ | $R_{sc} \le 1 k\Omega *$   |

| Short of both wires                               | R <sub>sc</sub> ≥ 100 kΩ                             | R <sub>sc</sub> ≤ 10 Ω   | R <sub>sc</sub> ≥ 100 kΩ | R <sub>sc</sub> ≤ 10 Ω   | $R_{sc} \ge 1 \text{ k}\Omega$  | R <sub>sc</sub> ≤ 100 Ω  | $R_{sc} \geq 1 \; k\Omega$      | R <sub>sc</sub> ≤ 100 Ω    |

| Open of single wire or<br>Single Termination lost | Not req.                                             | Not req.                 | R <sub>oc</sub> ≤ 2.5 Ω  | R <sub>oc</sub> ≥ 100 kΩ | R <sub>oc</sub> ≤ 20 Ω          | R <sub>oc</sub> ≥ 100 Ω  | R <sub>oc</sub> ≤ 20 Ω          | R <sub>oc</sub> ≥ 100 Ω    |

| Third Termination                                 | Not req.                                             | Not req.                 | Not req.                 | Not req.                 | R <sub>SC</sub> ≥ 1 kΩ          | R <sub>sc</sub> ≤ 100 Ω  | $R_{sc} \ge 1 \ k\Omega$        | R <sub>sc</sub> ≤ 100 Ω    |

| No Termination                                    | Not req.                                             | Not req.                 | Not req.                 | Not req.                 | Not req.                        | Not req.                 | R <sub>oc</sub> ≤ 20 Ω          | R <sub>oc</sub> ≥ 100 Ω    |

| Short of single wire to<br>GND or VBAT            | Not req.                                             | Not req.                 | Not req.                 | Not req.                 | Not req.                        | Not req.                 | R <sub>sc</sub> ≥ 10 kΩ         | $R_{sc} \leq 1 \; k\Omega$ |

<sup>\*(</sup>R<sub>SC\_PN</sub> < 10 Ω)

Short circuit voltage range is implementation specific and shall at least support 2V GND shift and up to 18V Battery supply

Table 7: HDD classes with their supported failure cases included.

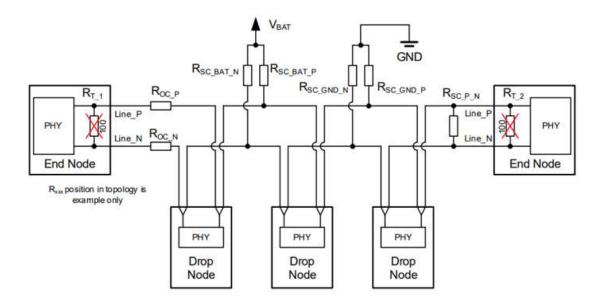

Figure 2 shows a simple summary of Table 7 with comparison of "hard / weak" failure with its resistive thresholds.

Figure 2: Summary HDD condition for "hard / weak failure"

During HDD measurement all other nodes shall be silent/transmitter high impedance.

It could be easier to apply this harness failures detection in a kind of diagnostic mode. The system implementer should design the system to ensure that the other nodes on the segment also enter a kind of passive mode to avoid disturbing the testing signals to be transmitted by the node performing the diagnostic.

## 9.2.2 HDD (HDD\_CTRL; HDD\_READY; START\_CTRL; VALID; SHORT\_OPEN\_ST) register

HDD is a summary of four HDD-subclasses (HDD1; HDD2; HDD3; HDD4) which are defined together with some status and control bits in the HDD register shown in Table 8.

| Register Name | HDD                      |

|---------------|--------------------------|

| Description   | Harness defect detection |

| size[bits]    | 16                       |

| MMD           | 31                       |

| Addr/Offset   | 0xCC01/0 *               |

<sup>\*</sup>In case PMD Transceiver is used for diagnostics in this specification the control register shall be at location x05 of PMD Transceiver.

| 15       | 14        | 13         | 12 | 11    | 10       | 9      | 8 |

|----------|-----------|------------|----|-------|----------|--------|---|

| HDD_CTRL | HDD_READY | START_CTRL |    |       | Reserved |        |   |

| RW       | RO        | RW/SC      |    |       | RO       |        |   |

| 7        | 6         | 5          | 4  | 3     | 2        | 1      | 0 |

| Reserved |           |            |    | VALID | SHORT_O  | PEN_ST |   |

| RO       |           |            |    |       | RO       | RC     | ) |

| Bit(s) | Name         | Description                                       | Access |

|--------|--------------|---------------------------------------------------|--------|

| 15     | HDD CTDI     | 0 - HDD not requested (Default)                   | RW     |

| 15     | HDD_CTRL     | 1 - HDD enable requested                          | KVV    |

| 1.4    | LIDD DEADY   | 0 – status feedback (HDD is not ready) (Default)  | RO     |

| 14     | HDD_ READY   | 1 – status feedback (HDD is ready)                | RO     |

|        |              | Write access:                                     |        |

|        |              | 0 - Start measurement not requested               |        |

|        |              | 1 - Start measurement enabled                     |        |

| 13     | START_CTRL   | Read access:                                      | RW/SC  |

|        |              | 0 - Measurement completed or aborted or not       |        |

|        |              | started (Default)                                 |        |

|        |              | 1 – Measurement in progress                       |        |

| 12:3   | Reserved     | Reserved (Default = 0)                            | RO     |

|        | VALID        | 0 – Measurement not valid. (Default)              |        |

| 2      | VALID        | 1 - Measurement results are ready and valid.      | RO     |

|        |              | Bus Short/Open Status:                            |        |

|        |              | 0 0 - no fault; everything is ok. (Default)       |        |

|        |              | 0 1 - detected as an open or missing              | DO.    |

| 1:0    | SHORT_OPEN_S | termination(s)                                    | RO     |

|        | Т            | 1 0 - detected as a short or extra termination(s) |        |

|        |              | 1 1 - fault but fault type not detectable         |        |

|        |              | More details can be available by vender           |        |

|        |              |                                                   |        |

Table 8: Definition of HDD register.

# 9.2.3 HDD\_CTRL field

| Field Name  | HDD_CTRL             |

|-------------|----------------------|

| Description | HDD enable requested |

| size[bits]  | 1                    |

| MMD         | 31                   |

| Addr/Offset | 0xCC01/15 *          |

<sup>\*</sup>In case PMD Transceiver is used for diagnostics in this specification the control register shall be at location x05 of PMD Transceiver.

| Field value | Explanation (HDD_CTRL)          |  |

|-------------|---------------------------------|--|

| 0x0         | 0 – HDD not requested (Default) |  |

| 0x1         | 1 – HDD enable requested        |  |

Table 9: Definition of HDD\_CTRL field in HDD register

## 9.2.4 HDD\_READY field

| Field Name  | HDD_READY                             |

|-------------|---------------------------------------|

| Description | Status feedback (HDD ready/nor ready) |

| size[bits]  | 1                                     |

| MMD         | 31                                    |

| Addr/Offset | 0xCC01/14 *                           |

<sup>\*</sup>In case PMD Transceiver is used for diagnostics in this specification the control register shall be at location x05 of PMD Transceiver.

| Field value | Explanation (START)                    |  |

|-------------|----------------------------------------|--|

| 0x0         | 0 – Status feedback (HDD is not ready) |  |

| 0x1         | 1 – Status feedback (HDD is ready)     |  |

Table 10: Definition of HDD\_READY field in the HDD register

## 9.2.5 START\_CTRL field

| Field Name  | START_CTRL        |

|-------------|-------------------|

| Description | Start measurement |

| size[bits]  | 1                 |

| MMD         | 31                |

| Addr/Offset | 0xCC01/13 *       |

<sup>\*</sup>In case PMD Transceiver is used for diagnostics in this specification the control register shall be at location x05 of PMD Transceiver.

| Field value | Explanation (START)                 |                                                 |  |

|-------------|-------------------------------------|-------------------------------------------------|--|

| 0x0         | Write access:                       | Read access:                                    |  |

|             | 0 - Start measurement not requested | Measurement completed or aborted or not started |  |

| 0x1         | Write access:                       | Read access:                                    |  |

|             | 1 – Start measurement enabled       | Measurement in progress                         |  |

Table 11: Definition of START\_CTRL field in the HDD register

## 9.2.6 VALID

| Field Name  | VALID                                   |

|-------------|-----------------------------------------|

| Description | Measurement results are ready and valid |

| size[bits]  | 1                                       |

| MMD         | 31                                      |

| Addr/Offset | 0xCC01/2 *                              |

<sup>\*</sup>In case PMD Transceiver is used for diagnostics in this specification the control register shall be at location x05 of PMD Transceiver.

| Field value | Explanation (VALID)                          |  |

|-------------|----------------------------------------------|--|

| 0x0         | 0 – Measurement not valid.                   |  |

| 0x1         | 1 – Measurement results are ready and valid. |  |

Table 12: Definition of VALID field in the HDD register

## 9.2.7 SHORT\_OPEN\_ST

| Field Name  | SHORT_OPEN_ST         |

|-------------|-----------------------|

| Description | Bus Short/Open Status |

| size[bits]  | 2                     |

| MMD         | 31                    |

| Addr/Offset | 0xCC01/1 *            |

<sup>\*</sup>In case PMD Transceiver is used for diagnostics in this specification the control register shall be at location x05 of PMD Transceiver.

| Field value | Explanation (SHORT_OPEN_ST)                       |

|-------------|---------------------------------------------------|

| 0x0         | 0 – no fault; everything is ok                    |

| 0x1         | 1 – detected as an open or missing termination(s) |

| 0x2         | 2 – detected as a short or extra termination(s)   |

| 0x3         | 3 – fault but fault type not detectable           |

Table 13: Definition of SHORT\_ST field in the HDD register

## 9.3 Dynamic Channel Quality

Dynamic channel quality includes the SQI diagnostic features with the two subclasses SQI, SQI+ and value.

## 9.3.1 SQI Transmit Opportunity ID (DCQ.TOID) register

The SQI value (8 levels), specified in 9.3.2 and the SQI+ value (8 to max. 256 levels), specified in 9.3.3, are determined for only a specific PLCA transmit opportunity or all as configured in DCQ.TOID. Multidrop mixing segments operating with PLCA enabled allow for the determination of a SQI or SQI+ value for each PHY transmit opportunity.

When this register is written (regardless of the previous value), the computation of DCQ.SQI and DCQ.SQI+ shall restart. Additionally, the DCQ.SQI.UPDATE field shall be reset.

| Register Name | DCQ.TOID                                         |

|---------------|--------------------------------------------------|

| Description   | DCQ Signal Quality Index Transmit Opportunity ID |

| size[bits]    | 16                                               |

| MMD           | 31                                               |

| Addr/Offset   | 0xCC02/0                                         |

| 15 | 14 | 13 | 12     | 11 | 10 | 9 | 8 |

|----|----|----|--------|----|----|---|---|

|    |    | Re | served |    |    |   |   |

|    |    |    | RO     |    |    |   |   |

| 7  | 6  | 5  | 4      | 3  | 2  | 1 | 0 |

|    |    | DC | Q.TOID |    |    |   |   |

|    |    |    | RW     |    |    |   |   |

| Bit(s)                                              | Name                                                      | Description Access     |    |  |

|-----------------------------------------------------|-----------------------------------------------------------|------------------------|----|--|

| 15:8                                                | Reserved                                                  | Reserved (Default = 0) | RO |  |

| 7:0                                                 | 7:0 DCQ.TOID Signal Quality Index Transmit Opportunity ID |                        |    |  |

| RO = read-only, RW = read-write, SC = self-clearing |                                                           |                        |    |  |

Table 14: Definition of register DCQ.TOID

## 9.3.1.1.1 DCQ.TOID field

| Field Name  | DCQ.DCQ.TOID                                 |  |  |  |

|-------------|----------------------------------------------|--|--|--|

| Description | nal Quality Index (Update current SQI value) |  |  |  |

| size[bits]  | 8                                            |  |  |  |

| MMD         | 31                                           |  |  |  |

| Addr/Offset | 0xCC02 / 0                                   |  |  |  |

| Field value | Explanation (DCQ.TOID)                                           |

|-------------|------------------------------------------------------------------|

| 0x00        | Compute SQI over packets received in PLCA transmit opportunity 0 |

| 0x01        | Compute SQI over packets received in PLCA transmit opportunity 1 |

| 0x02        | Compute SQI over packets received in PLCA transmit opportunity 2 |

|             |                                                                  |

| 0xFF        | Compute SQI over all received packets. (default)                 |

Table 15: Definition of TOID field in the DCQ register

## 9.3.2 SQI (DCQ.SQI.UPDATE; DCQ.SQI) register

## Diagnostic class SQI

The SQI value of eight levels shall be stored in a mandatory register (see section 9.3.2.2 DCQ.SQI).

It is open to the vendors, to implement in addition a second SQI register with min. 3 and max. 8 bits. For this optional DCQ.SQI+ register, if implemented, it is required to fulfill section 9.3.3.2 DCQ.SQI+.

| Register<br>Name | DCQ.SQI                  |

|------------------|--------------------------|

| Description      | DCQ Signal Quality Index |

| size[bits]       | 16                       |

| MMD              | 31                       |

| Addr/Offset      | 0xCC03 / 0               |

| 15      | 14           | 13 | 12 | 11       | 10 | 9  | 8 |

|---------|--------------|----|----|----------|----|----|---|

| SQI_UPD |              |    | F  | Reserved |    |    |   |

| RO      |              |    |    | RO       |    |    |   |

| 7       | 6            | 5  | 4  | 3        | 2  | 1  | 0 |

|         | Reserved SQI |    |    |          |    |    |   |

|         | RO           |    |    |          |    | RO |   |

| Bit(s) | Name     | Description                                                                                          | Access |

|--------|----------|------------------------------------------------------------------------------------------------------|--------|

| 15     | SQI_UPD  | SQI Update 0 – Update=0 (no change since last read) (Default) 1 – Update=1 (changed since last read) | RO     |

| 14:3   | Reserved | Reserved (Default = 0)                                                                               | RO     |

| 2:0    | SQI      | Signal Quality Index (current SQI value)                                                             | RO     |

Table 16: Definition of SQI field in the DCQ register

## 9.3.2.1 DCQ.SQI.UPDATE field

| Field Name  | DCQ.SQI.UPDATE                                |  |

|-------------|-----------------------------------------------|--|

| Description | gnal Quality Index (Update current SQI value) |  |

| size[bits]  | 1                                             |  |

| MMD         | 31                                            |  |

| Addr/Offset | 0xCC03 / 15                                   |  |

| Field value | Explanation (SQI_UPD)                                |

|-------------|------------------------------------------------------|

| 0x0         | 0 – Update = 0 (no change since last read) (Default) |

| 0x1         | 1 – Update = 1 (changed since last read)             |

Table 17: Definition of SQI.UPDATE field in the DCQ register

This bit is automatically cleared once read, or when DCQ.TOID is written.

Note that DCQ.SQI.UPDATE \* is mapped at addresses 0xCC03 and 0xCC04. These two aliases are effectively the same bit, meaning that when one is cleared, the other one shall be cleared too. This behaviour allows the host to read either the SQI or the SQI+ register collecting the DCQ.SQI.UPDATE information in a single read operation.

\* SQI: SQI or SQI+

## 9.3.2.2 DCQ.SQI (current SQI value) field

The SQI value of eight levels shall be stored in a 3bit register.

| Field Name DCQ.SQI                                   |            |  |  |

|------------------------------------------------------|------------|--|--|

| Description Signal Quality Index (current SQI value) |            |  |  |

| size[bits]                                           | 3          |  |  |

| MMD 31                                               |            |  |  |

| Addr/Offset                                          | 0xCC03 / 0 |  |  |

| Field value | Explanation (SQI)               |  |  |

|-------------|---------------------------------|--|--|

| 0x0         | - SQI=0 (worst value) (Default) |  |  |

| 0x1         | - SQI=1                         |  |  |

| 0x2         | 2 - SQI=2                       |  |  |

| 0x3         | 3 - SQI=3                       |  |  |

| 0x4         | 4- SQI=4                        |  |  |

| 0x5         | 5 - SQI=5                       |  |  |

| 0x6         | 6 - SQI=6                       |  |  |

| 0x7         | 7 - SQI=7 (best value)          |  |  |

Table 18: Definition of register field DCQ.SQI (8 levels)

## Correlation SQI to BER.

The recommended correlation between the SQI values stored in the register is based on AWG noise (bandwidth of 40 MHz) as shown in the Table 19 as well for information purposes.

| SQI with 3 bits (at least 8 levels)  Recommended BER for AWG noise model (informative) |                                                                                                    |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|                                                                                        | BER: Informative with the aim of calibrating SQI value of PHYs (Based on a defined test setup [4]) |

| SQI = 0                                                                                | BER > 10^-6                                                                                        |

| SQI = 1                                                                                | 10^-10 ≤ BER ≤ 10^-6                                                                               |

| SQI = 2                                                                                |                                                                                                    |

| SQI = 3                                                                                | BER < 10^-10                                                                                       |

| SQI = 4                                                                                |                                                                                                    |

| SQI = 5                                                                                |                                                                                                    |

| SQI = 6                                                                                |                                                                                                    |

| SQI = 7                                                                                | BER < 10^-12                                                                                       |

Table 19: Recommended correlation from SQI (at least 8 levels or 3 bits) to BER under AWG assumption.

The following features of the SQI value are mandatory:

- The indicated signal quality shall monotonically increase /decrease with noise (AWGN).

- The indicated SQI value shall be ≥ 3 for jitter ≤ 15ns @MDI (see [5]).

- SQI calculation shall be available in both PLCA and CSMA/CD mode.

- SQI Transmit Opportunity ID register is ignored in CSMA/CD mode.

In that case SQI is therefore calculated over all received packets.

A PHY implementation shall update the SQI value no later than when all the following conditions are met:

#### **Condition 1**

At least 16 Kbytes of data at the MAC layer has been received since the last SQI update.

## **Condition 2**

At least 32 carrier events (frames or bursts of frames) have been detected at the MAC layer since the last update.

## 9.3.2.2.1 Example to condition 1

#### **Example for 1 Transmitter and 1 Receiver:**

```

SQI_refresh_time_max(s) = 16kBytes/(Framerate<sup>1)</sup>(frame/s)*Framesize<sup>1)</sup>kBytes))

<sup>1)</sup>:of the Transmitter

```

#### Calculation example:

One head node and one drop node, both are sending one max. Ethernet frame during one PLCA cycle (2 max. Ethernet Frames during one PLCA cycle).

SQI\_(drop node sent to head node) calculated by head node = ?

```

Framesize(drop node) = Layer 1 Ethernet frame

= 1522Bytes

```

#### Framerate = 1 Frame / PLCA-Cycle-Time

- = 1 Frame / [2\*(preamble & SFD & payload & IPG) Bytes \* 8 <bit/Bytes> \* 100ns/bit]

- = 1 Frame / [2\*(1542Bytes+\*8 bit/Bytes \* 100ns/bit)] = 1/(2\*1,2336ms)

- = 405,3 Frames/s

```

SQI_refresh_time_max(s) = 16kBytes/(Framerate<sup>1)</sup>(frame/s)*Framesize<sup>1)</sup>kBytes))

= 16kBytes/(408,5 Frame/s *1,522kBytes/Frame)

= 25,9 ms

```

## **Example for multiple Transmitter and multiple Receiver:**

$Average\_SQI\_refresh\_time\_max(s) = 16kBytes/(Average\_Framerate^{2})(frame/s)*Average\_Framesize^{2}(kBytes)$

## Calculation example:

One Head node and 7 drop nodes, all are sending 5 max. Ethernet frames during every 7 PLCA cycle (8\*5 max. Ethernet Frames during 7 PLCA cycle, Average: 40/((7 max. Ethernet frames) during 1 PLCA cycle)

SQI\_(drop node ID1 sent to head node) calculated by head node = ?

```

Average_Framesize(drop node ID1) = Average Layer 1 Ethernet frame

= (5/7) * 1522 Bytes

= 1087,1 Bytes

Average_Framerate = 5 Frames / (7*PLCA-Cycle-Time)

```

- = 5 Frames / [7\*40\*(preamble & SFD & payload & IPG) Bytes \* 8 <bit/Bytes> \* Time/bit]

- = 5 Frames / [7\*40\*(1542 Bytes\*8 <bit/Bytes> \* 100ns)) = 5/ (7\*40\*1,2336ms)

- = 14,47 Frames/s

<sup>2):</sup> Average on the line

```

SQI_refresh_time_max(s) = 16kBytes/(Average_Framerate<sup>1)</sup>(frame/s)*Average_Framesize<sup>1)</sup>kBytes))

= 16kBytes/(14,46 Frame/s *1,522kBytes/Frame)

= 0.726 s

```

## 9.3.2.2.2 Example to condition 2

## **Example for 1 Transmitter and 1 Receiver:**

SQI\_refresh\_time\_max(s)=32\* FpB /Framerate(frame/s)

#### Calculation example:

Head node and drop node, both are sending one max. Ethernet frame (FpB = 1) during one PLCA cycle (2 max. Ethernet Frames during one PLCA cycle).

SQI\_(drop node sent to head node) calculated by head node = ?

```

Framesize(drop node) = Layer 1 Ethernet frame

```

= 1522Bytes

## Framerate = 1 Frame / PLCA-Cycle-Time

= 1 Frame / [2\*(preamble & SFD & payload & IPG) Bytes \* 8 <bit/Bytes> \* 100ns/bit]

= 1 Frame / [2\*(1542 Bytes + \*8 bit/Bytes \* 100 ns/bit)] = 1/(2\*1,2336 ms)

= 405,3 Frames/s

## SQI\_refresh\_time\_max(s) = 32\* FpB /Framerate(frame/s)

= 32\*1 / (408,5 Frame/s)

= 78,33 ms

## **Example for multiple Transmitter and multiple Receiver:**

```

Average_SQI_refresh_time_max(s) = 32 * \Sigma FpB(i) / \Sigma Framerate(i)_(frame/s)

```

#### Calculation example:

Head node and 7 drop nodes, all are sending 5 max. Ethernet frames during every 7 PLCA cycle.

- -> 8\*5 max. Ethernet Frames during 7 PLCA cycle

- -> Average: 40/7 max. Ethernet frames during 1 PLCA cycle

SQI\_(drop node ID1 sent to head node) calculated by head node = ?

```

Average_Framesize(drop node ID1) = Average Layer 1 Ethernet frame

= (5/7) * 1522Bytes

= 1087,1 Bytes

```

```

Average_Framerate = 5 Frames / (7*PLCA-Cycle-Time)

```

- = 5 Frames / [7\*40\*(preamble & SFD & payload & IPG) Bytes \* 8 <bit/Bytes> \* Time/bit]

- = 5 Frames / [7\*40\*(1542 Bytes\*8 <bit/Bytes> \* 100ns)) = 5/ (7\*40\*1,2336ms)

- = 14,47 Frames/s

Average\_SQI\_refresh\_time\_max(s) =

$$32 * \Sigma FpB(i) / \Sigma Framerate(i)_(frame/s)$$

=  $32 * (8*1) / (8*14,47 (frame/s))$

=  $2,21 s$

FpB = Frame per burst = PLCA\_burstcount + 1

Under the assumption that the total bandwidth required by the nodes is less than 10Mbit/s

## 9.3.2.2.3 Total results fulfilling both conditions 1 and 2

Example for 1 Transmitter and 1 Receiver: SQI\_refresh\_time\_max(s) = **78,33 ms**

Example for multiple Transmitter and multiple Receiver: SQI\_refresh\_time\_max(s) = 2,21 s

## Correlation SQI to BER.

The recommended correlation between the SQI values stored in the register is based on AWG noise (bandwidth of 40 MHz) as shown in the Table 19 as well for information purposes.

| SQI with 3 bits (at least 8 levels) | Recommended BER for AWG noise model (informative)                                                  |  |